基于1553B總線協議的解碼器設計和FPGA實現

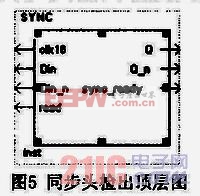

同步頭檢出模塊是檢測1553B三種類型字的同步頭。如圖2所示,命令字和狀態字的同步頭是先高電平后低電平,數據字的同步頭是先低電平后高電平,三種字的同步頭的高低電平各占1.5 μs。在用Verilog HDL硬件描述語言設計中,本文通過設置兩個計數器,分別在時鐘信號上升沿的時候給高低電平計數,理論上說兩個計數器都等于24的時候,同步頭才算檢出。但是要考慮到tco的影響,設計中當兩個計數器到等于22的時候,就說同步頭檢出,這時產生message ready信號,告訴狀態機要開啟數據處理模塊。如圖5所示,是同步頭檢出頂層圖。本文引用地址:http://www.104case.com/article/191237.htm

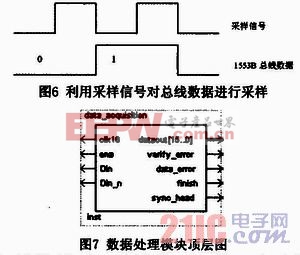

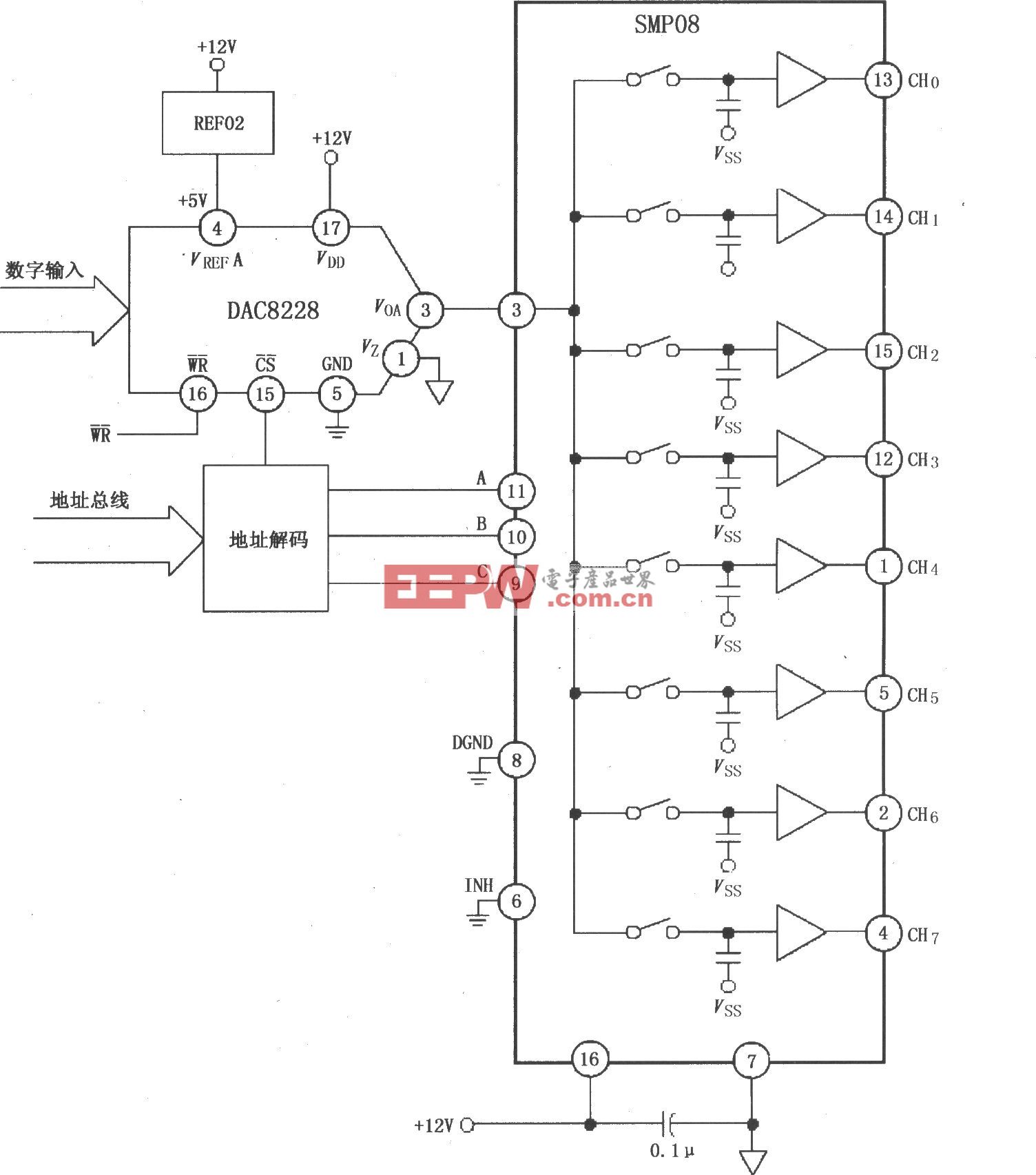

數據處理模塊是正確解碼后面的有效信息位,包括串并轉換、數據錯誤檢測、校驗位檢測。如圖6所示,利用把16MHz時鐘8分頻產生的2MHz的采樣信號對總線數據進行采樣,可以在每一碼位的1/4周期處和3/4周期處采樣,這樣采樣的信號最可靠。當一碼位兩次采樣的值不一樣時,就認為數據正確,并將第一次采樣的值發送給數據寄存器。如果一碼位兩次采樣的值相等,就認為數據錯誤,產生數據錯誤信號dataerror。當數據寄存器的前十六位的和除以2的余數等于第十七的數據時,就認為奇校驗正確。否則就認為錯誤,并產生奇校驗錯誤信號verify_error信號。圖7所示為數據處理頂層圖。

評論