基于FPGA和TFT彩屏液晶的便攜示波器設計

摘要:設計了以FPGA為核心采集模塊,以單片機為顯示控制核心,以TFT彩屏液晶為顯示器件的便攜數字存儲示波器。通過異步FIFO實現了FPGA中高速數據流與單片機處理速度之間的速率匹配。以三總線結構以及控制信號的握手協議為基礎,保證了FPGA與單片機通信的有效性和可靠性。該系統具有自動頻率控制(AFC)和自動增益控制(AGC)的功能,可以方便地對信號進行測量。

關鍵詞:FPGA;TFT液晶;異步FIFO;數字存儲示波器

在現代通信、雷達和航空航天等應用領域,由于設備復雜度和集成度的不斷增加,在進行外場維護和測試時,通常需要借助于示波器等一些輔助的電子測量儀器來觀察信號的波形并進行相關參數的測量。目前,現代化的數字存儲示波器以其獨特的優勢逐步取代了模擬示波器,對信號的測量帶來了很大的便利。然而,外場測試及維護工作的實際需要對示波器這樣的測量儀器也提出了更多的要求,除了成本的限制以外,在體積、精度、實時性以及使用的靈活性等方面也有了更高的標準。常用的示波器一般體積比較大,成本高,這就使它的應用受到了一些限制。在這種情況下,開發低成本便攜的手持示波器,將會大大提高其應用空間,為設備的外場維護和測試工作提供更多的便利。

本文針對實際需要,設計了以FPGA為核心采集模塊,以單片機為顯示控制核心,以TFT彩屏液晶為顯示器件的便攜數字存儲示波器。FPGA與高速A/D獲取波形采樣數據,通過單片機完成彩屏的初始化,合理設計出單片機與FPGA通信的總線握手協議,配合異步FIFO作為數據緩沖模塊,實現了邊采集邊顯示的效果。該系統具有小型化、操作簡單、采樣率高、動態范圍大、精度高、實時性強和波形顯示效果連續穩定的特點,同時還具有自動頻率控制和自動增益控制的功能,具有很廣闊的應用空間。

1 系統組成與工作原理

1.1 系統組成

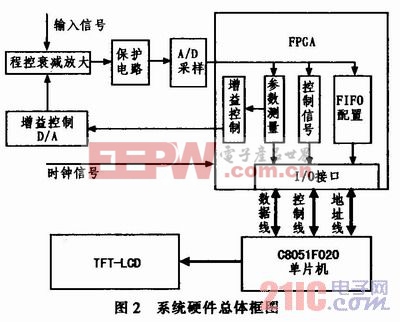

系統主要由信號調理電路、核心采集模塊、單片機處理模塊和液晶外圍電路組成。信號調理電路由繼電器、增益控制D/A、兩級可變增益放大器AD603和保護電路組成,主要用于對輸入信號進行程控的衰減與放大,使信號在最佳的測量和顯示量程范圍內。核心采集模塊以FPGA和高速A/D為核心,實現對信號的高速采樣處理以及與單片機的通信。單片機處理模塊接收波形數據并控制LCD進行譯碼顯示。液晶外圍電路為LCD提供合適的工作電壓,并對液晶模塊與單片機的接口電路進行設計。系統組成的總體框圖如圖1所示。

1.2 系統工作原理

根據輸入信號電平的范圍,FPGA發出控制信號控制調理電路的增益,將信號電平調整到最佳采集范圍。在FPGA內配置兩塊異步FIFO作為采集數據的緩存區,實現高速采集與單片機讀取速度之間的匹配。高速A/D在系統時鐘的驅動下采集波形數據,并由FPGA測出信號的電壓和頻率。根據信號頻率的不同,按照程序的預設選擇最佳的時基,控制FIFO的寫時鐘信號,而讀FIFO的時鐘信號則固定不變,這樣就可以在屏幕上得到最適合觀察的信號波形。該系統的量程設置和時基選擇完全由程序控制,不需要手動設置就可以自動將信號波形調整到最佳觀察狀態。

2 系統硬件設計

系統硬件主要實現對輸入信號的程控衰減放大、過壓保護,信號的采集處理,采集數據的傳輸以及單片機與液晶模塊接口電路等,系統硬件總體框圖如圖2所示。

評論