基于NAND FLASH的高速大容量存儲系統設計

3 系統設計

3.1 系統硬件結構組成

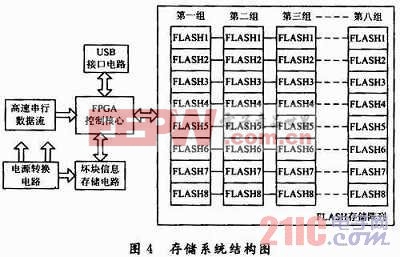

本文所設計的高速大容量存儲系統的結構框圖如圖4所示。系統中FLASH芯片選用三星公司的K9WBG08U1M,存儲陣列分為8組,采用流水線操作,每組由8片FLASH并聯共用控制線,各組對應行的FLASH共用數據線。系統存儲容量達到4×8×8=256 GB,存儲速度理論值為40MB/ s×8=320 MB/s。FPGA是整個系統的控制核心,它將產生各種復雜的邏輯時序來控制外圍芯片協調有序地工作,選用Altera公司StratixⅡ系列的EP2S60F484I4芯片,該芯片有48 352個邏輯單元,內置存儲RAM容量達2.5 MB,滿足緩存數據的要求。USB接口電路選用CYPRESS公司的CY7C68013A,該芯片集成了一個8.5 KB片上RAM的8051核、4 KB的FIFO以及USB 2.0收發器,滿足USB2.0通信協議,是進行USB2.0開發的常用芯片。壞塊信息存儲電路用于存儲和更新FLASH存儲陣列隨機出現的壞塊位置,它必須是非易失零出錯的存儲介質,因此選用AMD公司的Am29LV800B NOR型FLASH,存儲容量為8 Mb,保證無壞塊。本文引用地址:http://www.104case.com/article/191199.htm

3.2 系統具體實現

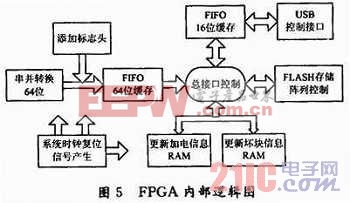

FPGA是整個硬件系統的核心,它完成電路的復雜時序控制,使系統有條不紊地運行。FPGA上電后進行初始化和加載配置信息,完成后進入工作狀態。首先根據USB接口電壓判斷是進入數據記錄狀態還是數據下載狀態,然后分別按照各自流程進行工作。FPGA內部邏輯設計如圖5所示。

由于FLASH存儲陣列是8片并聯一起操作,因此數據總線寬度便為64位,同時由于USB的接口數據寬度為16位,因此系統中使用了2個FIFO分別進行緩存。在系統記錄狀態下,前端接收到高速串行數據后首先進行串/并轉換,然后為其添加一個64位的標志頭一并存入FIFO緩存,標識頭是用來標記每次的加電情況,方便FLASH數據的分段下載。同時將外部NORFLASH內所存儲的壞塊信息讀入FPGA內部建立的RAM中,在總接口控制下,屏蔽FLASH存儲陣列內部的壞塊,并按一定順序將數據寫入FLASH芯片。由于數據在存儲過程中會產生新的壞塊,因此在每頁寫操作結束后需判斷此頁編程是否成功,若編程失敗,則對照此壞塊地址更新RAM中的壞塊信息,等待FLASH的存儲操作結束后,再將更新后的RAM數據寫入外部NOR FLASH進行保存。

在系統下載狀態時,首先對FLASH內部的存儲數據進行搜索,找到標識頭所在存儲陣列中的位置并將此位置信息寫入FPGA內部的RAM中,這樣便可知道每次加電后存儲數據在FLASH陣列中的起始塊位置和所占塊的容量。然后通過上位機軟件輸入起始位置,塊容量和下載命令后,FPGA內部的總接口控制便可根據這些命令信息,同時屏蔽壞塊后將FLASH存儲陣列中相應的數據寫入16位FIFO緩存中,隨后便可通過USB接口下載至計算機進行數據分析。

4 結語

隨著基于NAND技術的FLASH固態存儲器的快速發展,其存儲密度也越來越大,而體積、功耗和成本卻在減小,這使得NAND型FLASH在大容量高速存儲設備的研制中得到廣泛應用。本文針對單片FLASH存儲速度慢的缺點,將多片低速FLASH芯片并行起來工作,同時又運用流水線操作節省了FLASH的自身編程時間,從而使得整個存儲系統的存儲速度大大提高。針對NAND FLASH內部存在壞塊的問題,建立了一套完善的壞塊處理機制,使得系統能夠準確的存儲數據,保證數據的可靠性。使用FPGA對FLASH存儲陣列及USB下載電路進行控制,充分發揮了FPGA處理復雜邏輯的特點,簡化了系統的硬件結構。

評論