FPGA平臺實現最小開關損耗的SVPWM算法

當-π/3≤α≤π/3,零矢量,以為中心的30°區域的零矢量為,這樣三相橋臂就分別有著連續的60°的常開和常閉區域,三相橋臂的切換時間如表2所列,其中:Ta=Tx/2,Tb=Ty/2,Tc=(Tx+Ty)/2,Td=(T-(Tx+Ty))/2,Te=Td+Ta=(T-Ty)/2,Tf=Td+ Tb=(T-Tx)/2。本文引用地址:http://www.104case.com/article/191146.htm

這樣就可以使得負載功率因數角為0°的三相電流波形的峰值落在橋臂沒有開關動作的60°區域內,從而達到減小開關電流的目的。

3 Simulink仿真結果

根據前文所述理論,搭建Simulink仿真模型,三相逆變器的負載電阻R=5 Ω,負載電感L=0.5 mH,當逆變器的負載對稱平衡時,功率因子約為0.999,此時α近似為0°,直流電壓為690 V,調制比M=0.9,矢量空間被劃分為12個扇區。Simulink仿真模型算法模塊包括坐標變換模塊、扇區判斷模塊、扇區時間選擇模塊、橋臂時間切換模塊。

仿真結束后逆變器輸出3相的電流波形見本刊網站www.mesnet.com.cn——編者注。三相之間電流相差120°,矢量空間被分為12個扇區,在以a相電流峰值為中心的60°區域中,調制波為1或0,即a相橋臂是沒有開關動作的(常開或常閉)。仿真結果驗證了前文的理論分析。

4 基于FPGA的實現及實驗仿真結果

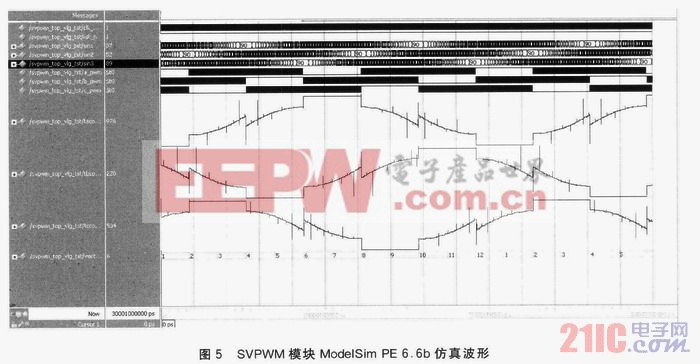

選擇Altera CycloneⅡ系列EP2C8Q208為FPGA的硬件核心,實現環境是QuartusⅡ9.0,FPGA硬件描述語言采用Verilog HDL,仿真環境ModelSim PE 6.6b。如圖5所示,三相調制波形相位與Simulnk仿真一致,調制波毛刺部分為FPGA內部邏輯延遲時間,小于FPGA所能識別的最小時間,對本系統的設計無影響。由圖中三相橋臂的上開關的控制信號可知,橋臂在一個開關周期內有120°的區域是沒有開關動作的(60°常開,60°常閉),因此系統的時序設計是正確可靠的,也驗證了上述理論以及Simulink仿真的正確性。

結論

本文實現了基于FPGA硬件平臺的最小開關損耗SVPWM算法。此算法相比于傳統SVPWM算法,在提高開關頻率的同時減少了開關損耗,可以根據實際負載的功率因子來判斷零矢量的選擇以及零矢量在扇區中的位置,控制橋臂開關的切換。FPGA硬件平臺的實現為今后實現更復雜的控制算法奠定了基礎,相比MCU/DSP,基于FPGA硬件實現的SVPWM有著更好的實時性能,其模塊化的設計也有著更好的靈活性,為進一步升級控制性能提供了便利。

評論