FPGA時(shí)鐘設(shè)計(jì)

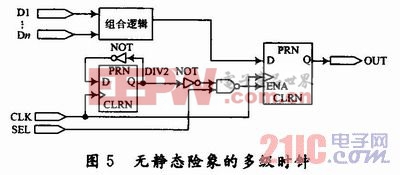

圖5給出圖4電路的一種單級(jí)時(shí)鐘的替代方案。圖中SEL引腳和DIV2信號(hào)用于使能D觸發(fā)器的使能輸入端,而不是用于該觸發(fā)器的時(shí)鐘引腳。采用這個(gè)電路并不需要附加PLD的邏輯單元,工作卻可靠多了。

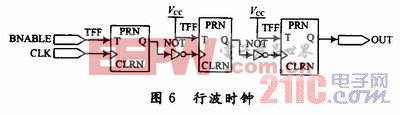

4 行波時(shí)鐘

另一種流行的時(shí)鐘電路是采用行波時(shí)鐘,即一個(gè)觸發(fā)器的輸出用作另一個(gè)觸發(fā)器的時(shí)鐘輸入。如果仔細(xì)地設(shè)計(jì),行波時(shí)鐘可以像鐘一樣地可靠工作。然而,行波時(shí)鐘使得與電路有關(guān)的定時(shí)計(jì)算變得很復(fù)雜。行波時(shí)鐘在行波鏈上各觸發(fā)器的時(shí)鐘之間產(chǎn)生較大的時(shí)間偏移,并且會(huì)超出最壞情況下的建立時(shí)間、保持時(shí)間和電路中時(shí)鐘到輸出的延時(shí),使系統(tǒng)的實(shí)際速度下降,如圖6所示。

評(píng)論