基于FPGA的NAND Flash ECC校驗

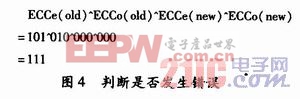

此時把所有4個ECC數值進行按位“異或”,就可以判斷是否出現了1個單一比特的錯誤或者是多比特的錯誤。如果計算結果為全“0”,說明數據在讀寫過程中未發生變化。如果計算的結果為全“1”,表明發生了1 bit錯誤,如圖4所示。如果計算結果是除了全“0”和全“1”的任何一種情況,那么就是2 bit出錯的情況。2 bit錯誤總可以檢測到,然而,Hamming碼算法僅能夠保證更正單一比特的錯誤。如果兩個或是更多的比特出錯,那么就不能修改該出錯的數據包,在這種情況下,Hamming算法就可能不能夠指示出已經出現的錯誤。不過,考慮到SLC NAND器件的比特錯誤的情況,出現2、3 bit錯誤的可能性非常低。本文引用地址:http://www.104case.com/article/191099.htm

對于1 bit錯誤的情況,出錯地址可通過將原有ECCo值和新ECCo值進行按位“異或”來識別獲取。通過圖5中的計算,結果為2,表明原數據第2 bit位出現了問題。該計算采用奇校驗數據ECCo,這是因為它們可以直接地反映出出錯比特的位置。

![]()

找到出錯比特后,只要通過翻轉它的狀態就可修復數據包,具體操作也就是將該位與“1”進行異或操作,如圖6所示。

![]()

2 擴展數據包

在上述舉例中,校驗1個8 bit數據包需要6 bit的ECC數據。在這種情況下,校驗數據量達到原始數據包的數據量的75%,看上去并不令人滿意。然而,隨著數據包大小的增加,Hamming算法將表現得越來越有效率。由前面2n bit數據需要2n bit ECC校驗的關系推知,每增加一倍的數據要求兩個額外的ECC信息比特。這樣,當數據增加到,比如512 Byte時,僅產生24 bit的ECC,此時用于校驗的數據占原數據的比例降為0.06%,效率較高。下面,以1個8 Byte的數據包為例說明擴展數據包的校驗情況。

在這里,由于異或操作滿足交換律,用一種更為有效的方法進行校驗。如圖7所示,首先將該8 Byte數據排為1個矩陣的形式,每行為1B-yte。分別計算每行各bit的異或結果記為字節校驗碼(Byte-Wise),計算每列各bit的異或結果記為比特校驗碼(Bit-Wise)。接下來,將兩個校驗碼分別按上述方法分割計算得到ECC校驗碼,并將字節校驗碼的ECC結果作為ECCe和ECCo的高有效位(MSB)、比特校驗碼的ECC結果做為低有效位(LSB)進行組合,最終得到8 Byte數據包的ECC校驗碼。

評論