基于FPGA的存儲測試系統(tǒng)的設(shè)計

設(shè)計可選采樣頻率有八種,如圖3中1 MHz~1 kHz,都是由FPGA的時鐘模塊分頻而來,可根據(jù)實際情況修改。S1、S2為環(huán)境選擇信號;P0~P2、P3~P5、P6~P8三組信號分別是三個環(huán)境的采樣頻率控制字,在測試前根據(jù)環(huán)境采樣頻率的需要來編程設(shè)定;模塊mux8為8選1數(shù)據(jù)選擇器,根據(jù)輸入的三個控制字來選擇對應(yīng)的采樣頻率輸出。系統(tǒng)上電后,環(huán)境選擇信號S1、S2為“00”,模塊mux3將1環(huán)境的采樣頻率控制字P0、P1、P2輸入到模塊mux8中,系統(tǒng)自動以1環(huán)境的采樣頻率進(jìn)行采樣;2環(huán)境的觸發(fā)信號到來時,S1、S2由“00”跳變?yōu)?ldquo;10”,2環(huán)境的采樣頻率控制字P3~P5送到mux8中,以2環(huán)境的采樣頻率進(jìn)行采樣;當(dāng)3環(huán)境的觸發(fā)信號來臨,S1、S2由“10”跳變?yōu)?ldquo;11”,3環(huán)境的采樣頻率控制字P6~P8被選中,系統(tǒng)以3環(huán)境的采樣頻率采樣。

3 實驗驗證

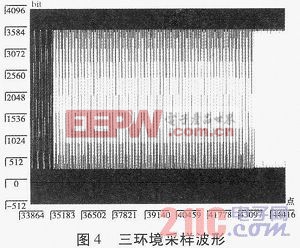

該實驗對標(biāo)準(zhǔn)信號發(fā)生器輸出的正弦波信號進(jìn)行采集和存儲,采樣策略選擇為三環(huán)境采樣,1環(huán)境采樣頻率為1 MHz,2環(huán)境為100 kHz,3環(huán)境為50 kHz,外觸發(fā)進(jìn)入1環(huán)境,計數(shù)觸發(fā)進(jìn)入2環(huán)境,計數(shù)值128 kW,計數(shù)觸發(fā)進(jìn)入3環(huán)境,計數(shù)值32 kW。系統(tǒng)采樣完畢后,連接到計算機(jī)通過上位機(jī)軟件讀取數(shù)據(jù),實驗波形如圖4。本文引用地址:http://www.104case.com/article/191009.htm

設(shè)置為計數(shù)128 kW進(jìn)入2環(huán)境,計數(shù)32 kW進(jìn)入3環(huán)境,而系統(tǒng)負(fù)延遲為8 kW,分為4個通道,因此1、2環(huán)境的分界點為(128+8)·1024/4=34816點,2、3環(huán)境的分界點為(128+8+32)*1024/4=43008點,實驗波形與計算值相符。如表1所示:

通過上表可以看出,系統(tǒng)變頻采樣模塊的設(shè)計滿足系統(tǒng)的要求,并且系統(tǒng)是完全按照設(shè)定的采樣策略進(jìn)行采樣的。

4 結(jié)束語

介紹了一種用FPGA實現(xiàn)的動態(tài)測試存儲測試系統(tǒng)。通過實驗驗證,表明系統(tǒng)能對信號進(jìn)行不失真采樣存儲。證實了所設(shè)計的采樣策略對多種變化規(guī)律的信號采集具有通用性,實現(xiàn)了對信號的變頻采樣,擴(kuò)展了系統(tǒng)的應(yīng)用范圍。

評論