基于FPGA的存儲測試系統的設計

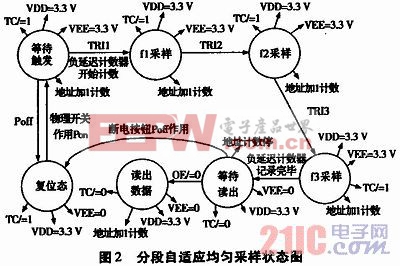

根據被測信號頻率變化很大的特點,設計如圖2所示的狀態圖,實現對此類信號的變頻采樣。測試系統分環境對信號采樣記錄,每個環境的采樣頻率可以在采樣前進行設置,本系統設計為三個環境,即采樣頻率最多變化三次。本文引用地址:http://www.104case.com/article/191009.htm

在存儲測試開始之前,通過軟件編程將采集存儲過程分為幾個階段,根據被測信號的變化,每一個階段的采樣頻率、存儲點數、采樣開始時間會作自適應的調整。首先接通電源使電路處于復位態,此時數字電源VDD為通電、模擬電源VEE為斷電狀態,系統中只有FPGA控制模塊工作;然后對電路編程設定各個環境的采樣頻率,給電路上電,電路進入等待觸發態,此時VDD、VEE通電,存儲器、AD轉換器啟動,開始采樣,地址計數器開始工作;觸發信號TRI1到來后,進入f1采樣態,系統按編程設定的采樣頻率f1開始采樣,負延遲計數器開始工作;2環境觸發后,系統按照設定的采樣頻率f2進行采樣,此時處于f2采樣態;3環境觸發后,系統按采樣頻率f3采樣,處于f3采樣態;當負延遲計數器計滿設定值時,地址計數器和負延遲計數器均停止工作,VEE斷電,系統進入等待讀出態;在讀出數據態,地址同步推進,直到讀完所有的數據。

2.2 變頻采樣的模塊設計

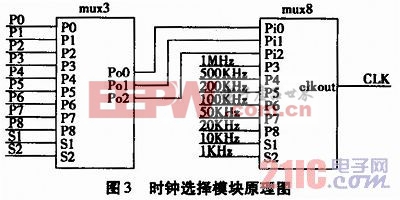

采樣頻率決定了采樣信號的質量和數量,采樣頻率太高,會使采得的信號數量劇增,占用大量的存儲單元,采樣頻率太低的話,會使模擬信號的某些信息丟失,恢復出的信號會出現失真。為了達到最佳效果,必須根據信號的特點選擇合適的采樣頻率。圖3為設計的采樣時鐘選擇模塊。

評論