全加器功能及應用的仿真設計分析

3.3 全加器功能應用仿真設計

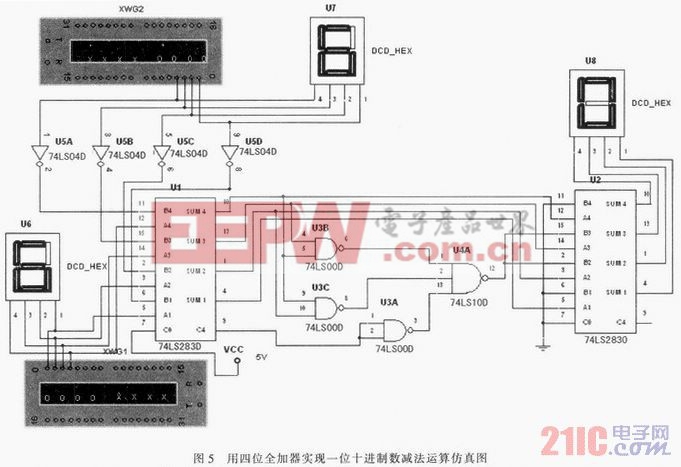

全加器除了可完成二進制加法運算外,還可以實現二進制減法運算、乘法運算,BCD碼的加、減法,碼制轉換,數碼比較,奇偶校驗等應用。用集成全加器74LS283實現兩個一位8421碼十進制數的減法運算功能仿真,如圖5所示。本文引用地址:http://www.104case.com/article/191007.htm

根據減去一個正數,等于加上一個負數的概念,將一位十進制數的減法變成加法。在數字電子技術中,這種運算可以用機器數的原碼、反碼、補碼來實現。對于一個正數其原碼、反碼、補碼是一樣的,而對于一個負數其補碼是在原碼基礎上符號位不變,其余各位取反為反碼,再在最低位加1形成的。原碼、反碼在計算后都要進行修正,而補碼符號位進位自然丟失,可直接還原出真值。

圖5中全加器的加數B4、B3、B2、B1,是由字信號發生器輸出經反相器(按位取反)后輸入的。并且全加器最低位進位設為1,實現了按位取反再加1,組成A減B的運算電路。

利用補碼轉換為加法運算后,8421碼十進制數的計數規律是逢十進一,而全加器74LS283是四位二進制逢十六進一,兩者進位關系不同,當和數大于9時8421碼產生進位,而十六進制不產生。為此,由74LS00和74LS10構成結果修正電路。當和數大于9時,該電路輸出1,為加法運算增加修正數6(第二個全加器的加數B=0110)實現進位。當和數小于9時,該電路輸出0,修正數為0。從測試結果得知,此電路實現具有修正功能的一位8421碼十進制減法運算。圖5中顯示6-6=0。在仿真測試時,兩個字信號發生器的地址參數設定為0000-0009。

4 結束語

Multisim仿真軟件為工程技術設計仿真、電子技術教學、實訓、演示提供了強大、靈活、便捷、生動的虛擬仿真工具。通過對全加器功能及應用的虛擬仿真設計、測試、分析,既熟練掌握仿真軟件中儀器儀表的使用,也鍛煉分析問題解決問題的能力,同時還能準確地驗證所設計仿真測試的內容和方法,為進一步利用Multisim軟件開發設計仿真新項目打下基礎。

評論