EEPW首頁(yè) >>

主題列表 >>

全加器

全加器 文章 最新資訊

用兩個(gè)全加器構(gòu)成二一十進(jìn)制相減器

- 用兩個(gè)全加器構(gòu)成二一十進(jìn)制相減器

- 關(guān)鍵字: 全加器 二一十進(jìn)制 相減器

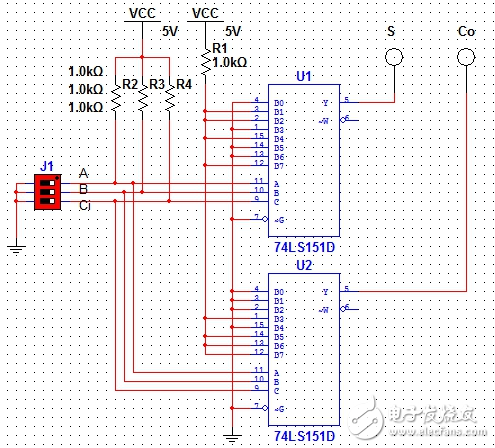

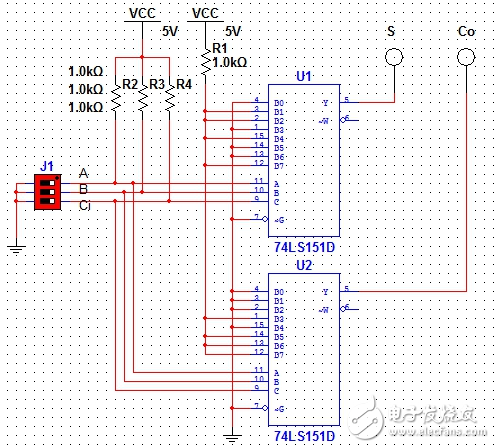

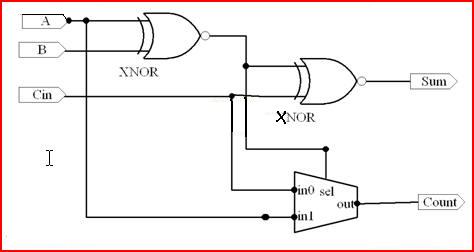

全加器功能及應(yīng)用的仿真設(shè)計(jì)分析

- 摘要:加法運(yùn)算是數(shù)字系統(tǒng)中最基本的算術(shù)運(yùn)算。為了能更好地利用加法器實(shí)現(xiàn)減法、乘法、除法、碼制轉(zhuǎn)換等運(yùn)算,提出用Multisim虛擬仿真軟件中的邏輯轉(zhuǎn)換儀、字信號(hào)發(fā)生器、邏輯分析儀,對(duì)全加器進(jìn)行功能仿真設(shè)計(jì)、轉(zhuǎn)

- 關(guān)鍵字: 全加器 仿真設(shè)計(jì) 分析

基于多數(shù)決定邏輯非門(mén)的低功耗全加器設(shè)計(jì)

- 全加器是算術(shù)運(yùn)算的基本單元,提高一位全加器的性能是提高運(yùn)算器性能的重要途徑之一。首先提出多數(shù)決定邏輯非門(mén)的概念和電路設(shè)計(jì),然后提出一種基于多數(shù)決定邏輯非門(mén)的全加器電路設(shè)計(jì)。該全加器僅由輸入電容和CMOS反向器組成,較少的管子、工作于極低電源電壓、短路電流的消除是該全加器的三個(gè)主要特征。對(duì)這種新的全加器,用PSpice進(jìn)行了晶體管級(jí)模擬。結(jié)果顯示,這種新的全加器能正確完成加法器的邏輯功能。

- 關(guān)鍵字: 邏輯 非門(mén) 低功耗 全加器

一種結(jié)構(gòu)簡(jiǎn)單的低壓低功耗ALU單元設(shè)計(jì)

- 1.引言 隨著手持式個(gè)人通訊系統(tǒng)等的發(fā)展,低壓低功耗高吞吐量電路的需求越來(lái)越多,因此低功耗微處理器和元件的設(shè)計(jì)已經(jīng)變成了主流。ALU是微處理器最重要的組成部分,其中全加器電路是所有運(yùn)算電路的基本單元,設(shè)計(jì)低功耗快速加法器單元是獲得低功耗高速運(yùn)算電路的關(guān)鍵。ALU單元的設(shè)計(jì)標(biāo)準(zhǔn)是多種多樣的,晶體管數(shù)量顯然是一個(gè)主要的關(guān)注點(diǎn),因?yàn)樗鼧O大的影響了功能單元ALU的設(shè)計(jì)復(fù)雜性。另外兩個(gè)重要的卻又相互矛盾的因素是功耗和速度。與功耗降低相關(guān)的一個(gè)因素是電路能工作的最低電壓, 還有一個(gè)是晶體管的數(shù)量,而全加器晶

- 關(guān)鍵字: 低功耗 ALU 微處理器 全加器

等價(jià)型PG邏輯及其在加法器設(shè)計(jì)中的應(yīng)用

- 摘 要:全加器實(shí)現(xiàn)的基本原理是基于進(jìn)位傳播和進(jìn)位產(chǎn)生的PG邏輯。根據(jù)現(xiàn)有的PG邏輯計(jì)算公式,本文推導(dǎo)出一種新的等價(jià)型邏輯表達(dá)式,并驗(yàn)證了其正確性。將該等價(jià)型邏輯表達(dá)式用于全加器的設(shè)計(jì)中,能夠改變?cè)械娜悠鹘Y(jié)構(gòu),并改變布線通道的連線數(shù)目和連線方式。 關(guān)鍵詞:全加器;PG邏輯;連線;負(fù)載 引言 在全加器設(shè)計(jì)中運(yùn)用PG邏輯是非常普遍的,本文在設(shè)計(jì)和研究全加器時(shí),根據(jù)現(xiàn)有的PG邏輯公式推導(dǎo)出了一種新的邏輯公式,并論證了兩者之間的等價(jià)關(guān)系。這一新的公式能夠指導(dǎo)全加器設(shè)計(jì)中的連線方式,靈活更改

- 關(guān)鍵字: 嵌入式系統(tǒng) 單片機(jī) 全加器 PG邏輯 連線 負(fù)載 放大器

| 共6條 1/1 1 |

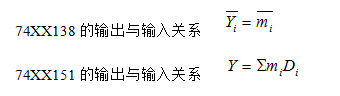

全加器介紹

一位全加器 全加器是能夠計(jì)算低位進(jìn)位的二進(jìn)制加法電路

一位全加器(FA)的邏輯表達(dá)式為:

S=A⊕B⊕Cin

Co=AB+BCin+ACin

其中A,B為要相加的數(shù),Cin為進(jìn)位輸入;S為和,Co是進(jìn)位輸出;

如果要實(shí)現(xiàn)多位加法可以進(jìn)行級(jí)聯(lián),就是串起來(lái)使用;比如32位+32位,就需要32個(gè)全加器;這種級(jí)聯(lián)就是串行結(jié)構(gòu)速度慢,如果要并行快速相加可以用超前進(jìn)位加法,

[ 查看詳細(xì) ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司