基于FPGA與ARM的遙測數據網絡化采集

2.1 幀同步模塊

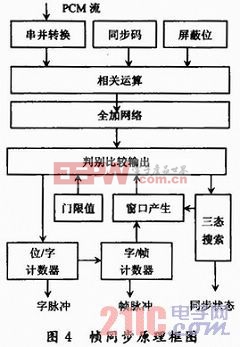

幀同步器根據幀同步碼組的相關性和周期性,經過相關運算將同步碼從PCM串行流中識別出來,原理框圖如圖4所示。本文引用地址:http://www.104case.com/article/190977.htm

PCM數據按時鐘進行串/并轉換,與本地幀同步碼進行同或運算后再與上屏蔽位,由全加網絡將相關運算結果按位相加統計結果中1的個數,大于門限值則表示可能接收到了幀同步碼。

為避免虛警和漏檢,使幀同步器穩定可靠工作,采用搜索、校核、鎖定三態邏輯。

系統開始時處于搜索態,符合相關器輸出,由搜索態轉入校核態。在預期檢測窗口內沒有幀碼,從校核返回到搜索態。連續通過校核數α,進入鎖定態。為避免幀同步碼的漏檢,連續漏檢超過保護幀數β,幀同步才返回搜索態,否則保持在鎖定態,幀脈沖由本地產生。

2.2 IRIG—B碼解調

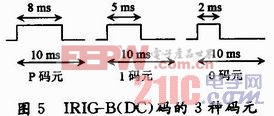

IRIG時間序列碼是一種串行碼,共有3種碼元,如圖5所示。

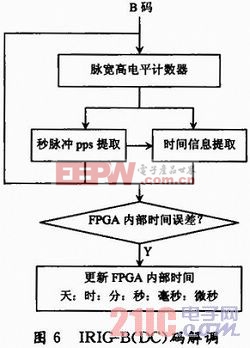

P碼元是位置碼元,連續2個P碼為一幀的開始,第1個P碼元定義為P0,第2個P碼元為秒脈沖pps,上升沿為該秒的準時刻,時間信息以BCD碼依次分布在其后的碼元中。解調時先進行pps的提取,再進行秒、分、時、天的信息提取,其流程如圖6所示。

時鐘頻率為1 MHz,用計數器對輸入信號的脈寬進行計數。8 ms,5 ms,2 ms脈寬計數為8 000,5 000,2 000。輸入B碼的脈寬會混有干擾,晶振時鐘也存在一定的誤差,計數器的計時判別應浮動一個范圍,設置門限為脈寬的85%~115%,當滿足一定范圍的數值時,分別輸出P碼,0碼,1碼信號。

FPGA中的時碼產生“天:時:分:秒:毫秒:微秒”信息。解調出B碼時,FPGA更新內部時間,B碼中不含毫秒與微秒信息,由FPGA根據秒脈沖信息的準時刻來生成。

3 FPGA驅動程序開發

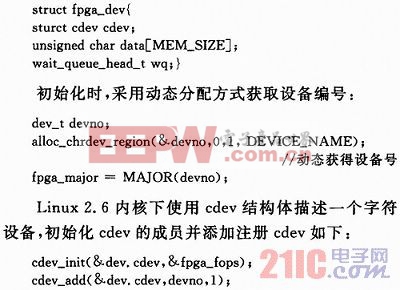

在Linux中,所有的硬件設備都像常規文件一樣進行打開、關閉和讀/寫。把FPGA當作字符設備進行設計,驅動由設備加載與卸載,以及文件操作file_operation結構體中成員函數組成。

3.1 加載與卸栽設備驅動

FPGA設備驅動程序初始化流程為動態獲得主設備號、字符設備注冊和申請中斷;卸載流程為注銷設備,釋放設備編號。

定義一個設備結構體來表示FPGA,如下:

評論