一種新的基于FPGA的數據格式轉換方法

3 仿真結果及分析

首先用ModelSim進行功能仿真,其結果如圖3所示。輸入的實數為125.763,輸出結果經Matlab逆向求值同輸入值進行比較,驗證了轉換結果的正確性。一個數的正確轉換并不能說明問題,下面將驗證此轉換方法的可行性。本文引用地址:http://www.104case.com/article/190975.htm

選取具有代表性的實數對轉換方法的性能進行驗證。主要驗證兩個方面:

(1)是否在預定域內具有全覆蓋性;

(2)是否能對此域中的最小值進行有效表示。

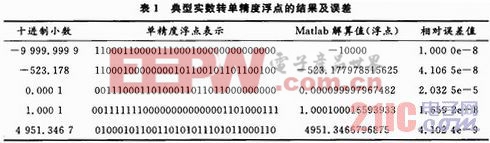

結果如表1所示。

根據轉換原理,最小值所轉換的誤差最大,但最大值的轉換誤差不一定最小(因為存在舍入)。這個最大的轉換誤差在10-5量級,當待轉換實數的絕對值大于整數1時,轉換的誤差將小于10-5量級,可達10-9量級。這樣的轉換誤差可以滿足大多數浮點運算環境下的精度需要。實驗驗證了此轉換方法的有效性和“全覆蓋性”。

在完成仿真測試后,將程序進行綜合,布局布線,最后生成位流文件下載到FPGA芯片中進行驗證。在實際的芯片中將轉換結果和已仿真得到的結果進行比較,并輸出指示信號。從實際的電路輸出結果看,和仿真結果完全一致,證明了此方法在實際芯片中可行性。因為采用的是流水線操作,所以仿真所用的周期數和實際周期數是一致的。該實驗在50 MHz的時鐘下用時6個周期(即0.12μs)完成轉換操作。而在最常用的串口傳輸波特率9 600 b/s下,傳送1個碼元的時間為10-1ms量級。從而可以得出:完成從ASCII碼所表示的實數(-9 999.999 9~+9 999.999 9)到單精度浮點的轉換所用的時間將在10-1μs量級以下,具有較高的實時性。

4 結語

本文使用ISE 9.1i和ModelSim軟件平臺,選用Spartan 3E XC3SS00E FPGA芯片,采用VHDL硬件描述語言,對系統進行了功能仿真和下載驗證,并借助MATLAB軟件對轉換結果進行驗證分析。從實驗結果看,將范圍在-9 999.999 9~+9 999.999 9的實數轉換為單精度浮點數表示所產生的誤差可以滿足大多數浮點運算環境下的精度要求;在時鐘為50 MHz的情況下,轉換所用時間為10-1μs量級,完全可以滿足非特殊情況的高速數字信號處理。本文的實現向單精度浮點的轉換占用1 161個slice資源,在FPGA發展到今天,FPGA的容量和資源都有了很大提高的情況下,這樣的資源占用量在大多數應用中是可以承受的。本文的設計可以很容易地根據實際實數的范圍進行調整,并且可以推廣到其他浮點格式,可有效地為浮點IP核提供快速且具有高精度的數據源。

評論