一種新的基于FPGA的數據格式轉換方法

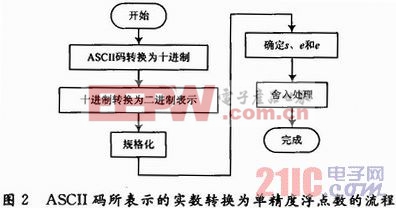

2 在FPGA中實現實數到單精度浮點數轉換的流程

2.1 轉換流程

在實際工程應用中,所處理的數據都有一個或大或小的范圍,在這個范圍內將實數轉換為單精度浮點數會節約芯片資源和降低功耗。故選擇在-9 999.999 9~9 999.999 9的范圍內完成實數到單精度浮點數的轉換,如圖2所示。考慮到實際,數值在很多情況下是通過串口獲取的,并表現為ASCII形式。故本文中所提到的實數皆為ASCII表示。本文引用地址:http://www.104case.com/article/190975.htm

轉換過程采用流水線操作,用計數器控制轉換進程。ASCII碼轉換為單精度浮點的方法如下:

(1)將8位ASCII碼所代表的數字字符轉為十進制數字(由于硬件電路對數字的表示只有0和1的組合,所以將實數的整數和小數分開表示);

(2)利用程序包里的數據類型轉換函數將十進制數轉換為二進制數,但小數部分的轉換需要單獨實現;

(3)對二進制表示的實數進行規格化;

(4)根據符號位ASCII碼值確定符號位s,根據規格化移動的位數確定階碼e,將規格化中的小數部分f保留28位;

(5)根據就近舍入原則對保留的28位小數部分的后5位進行判斷和舍入。

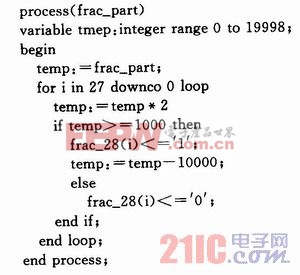

2.2 關鍵代碼解析

在FPGA的硬件描述語言中將整數的十進制轉換為二進制比較簡單,可以調用ISE軟件自帶的程序包中的轉換函數來實現,但如何將小數部分轉換為二進制是能否順利完成從實數到單精度浮點數轉換的關鍵。考慮到要對小數部分進行舍入運算,所以將小數部分轉換28位的二進制。要用28位二進制表示小數部分,需利用VHDL語言中變量(variable)被賦值時立即生效的特性,結合FOR循環來實現。部分關鍵代碼如下:

代碼中frac_part是小數部分的十進制表示(因為integer類型只能表示整數,所以將小數部分擴大了10 000倍,但不影響結果的正確性),frac_28是小數部分的二進制表示。信號frac_28(27)的權值是2-1,依次以1/2倍率遞減,frac_28(0)的權值是2-28。此進程由frac_part發生變化來啟動,完成轉換的時間是瞬時,也可以認為是一個時鐘周期。

評論