下面對2個3:2 CSA壓縮器合并成一個6:4壓縮器單元運(yùn)算邏輯做理論推導(dǎo),其中:

,形成一個直通電路。本文引用地址:http://www.104case.com/article/190974.htm

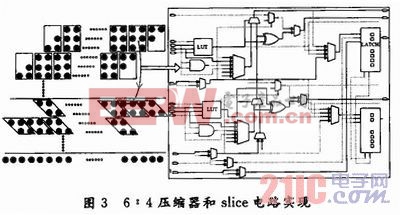

從圖3可以看出,WALLACE TREE的6:4壓縮器單元只用一個slice就可以實現(xiàn)。而幾乎所有Xilinx的FPGA器件內(nèi)部slice結(jié)構(gòu)都類似,因此該6:4壓縮器在基本的FPGA器件中都可以通過此手動編輯方法實現(xiàn),形成一個可供頂層WALLACETREE邏輯調(diào)用的硬宏模塊。

評論