利用FFT IP Core實現(xiàn)FFT算法

3.1 FFT 運算器

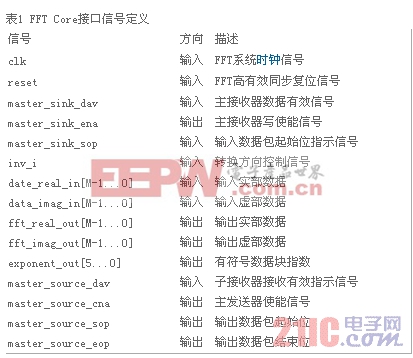

FFT運算器采用FFT Core實現(xiàn),其引擎結(jié)構(gòu)為雙Single-output,I/O數(shù)據(jù)流采用突發(fā)(Burst)方式。FFT Core采用Atlantic Interface協(xié)議,輸入

接口視為主接收器,輸出接口視為主發(fā)送器。具體接口定義如表1所示。

具體的工作流程:系統(tǒng)復(fù)位后,數(shù)據(jù)源將master_sink_dav置位,表示有采樣數(shù)據(jù)等待輸入;作為回應(yīng),F(xiàn)FT Core將master_sink_ena置位,表示可以接收輸入數(shù)據(jù);數(shù)據(jù)源加載第一個復(fù)數(shù)數(shù)據(jù),同時master_sink_sop置位,表示輸入數(shù)據(jù)塊的起始;下一個時鐘,master_sink_sop被清零,輸入數(shù)據(jù)按照自然順序被加入。輸入數(shù)據(jù)達(dá)到256點時,系統(tǒng)自然啟動FFT運算。通過inv_i信號的置位/清零可以改變單個數(shù)據(jù)塊的FFT轉(zhuǎn)換方向,inv_i信號必須和master_sink_sop信號嚴(yán)格同步。當(dāng)FFT轉(zhuǎn)換結(jié)束時,子接收器已經(jīng)將master_source_dav信號置位,表示子接收器可以接收FFT的轉(zhuǎn)換結(jié)果;同時,master_source_ena信號置位,F(xiàn)FTCore按照自然順序輸出運算結(jié)果;在輸出過程中,

master_source_sop和master_source_eop信號被置位,表示輸出數(shù)據(jù)塊的起始和結(jié)束。詳細(xì)的描述參見文獻[4]。

3.2 控制器與后處理單元

控制器大體可分為三個部分:輸入緩沖控制(c_i)、FFT運算控制(c_f)、輸出緩沖控制(c_o)。c_i為輸入緩沖器提供讀/寫地址和相應(yīng)的讀/寫

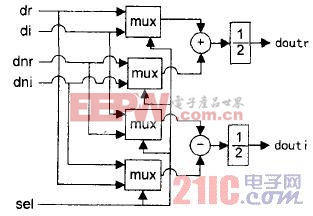

控制信號;c_f為FFT運算器提供控制信號,嚴(yán)格控制FFT Core的工作時序;c_o為輸出緩沖器提供讀/寫地址及讀/寫控制信號。控制器通過VHDL語言編程的狀態(tài)機方式可以輕易實現(xiàn)。后處理單元其實是式(2)和式(3)的硬件實現(xiàn),具體的原理如圖2所示。

圖2后處理單元原理圖

圖中標(biāo)識“mux”、“+”、“-”、“1/2”分別表示選擇器、加法器、減法器和除法器,dr、di、dnr、dni分別與式(1)和式(2)中的Zr(k)、

Zi(k)、Zr(N-k)、Zi(N-k)相對應(yīng)。當(dāng)sel等于0時,提取第一路實序列的頻譜數(shù)據(jù)G(k),實現(xiàn)式(1)功能;當(dāng)sel等于1時,提取第二路實序列的頻譜數(shù)據(jù),實現(xiàn)式(2)功能。

評論