基于FPGA的數字積分法插補控制器設計與實現

(2)位置計數器

位置計數器有3個寄存器,分別對應于三個軸。其初始值為需要插補的脈沖數目。當積分器每輸出一個脈沖,計數器便做減“1”。當位置計數器為零時,則表示到達終點坐標位置,插補結束。

(3)插補積分器

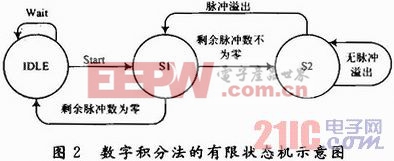

插補積分器是直線插補的核心模塊,由余數寄存器和被積函數寄存器構成。被積函數寄存器中存放由數據緩存器提供的終點坐標值,每當脈沖源發出1個插補迭代脈沖時,被積函數寄存器與余數寄存器的值累加1次,并將累加結果存放余數寄存器中,當累加結果超出余數寄存器容量(216)時,溢出1個脈沖。經過N=216次累加后,每個坐標軸的溢出脈沖總數就等于該坐標的被積函數值。在余數寄存器的容量一定的情況下,其輸出脈沖頻率與終點坐標值的大小成正比。控制器采用三軸聯動,則同時有3個積分器同時進行插補運算。在該插補控制器的設計中,采用有限狀態機的原理完成直線插補的實現,如圖2所示,共有3個狀態存在:本文引用地址:http://www.104case.com/article/190545.htm

(1)狀態IDLE:空閑狀態,等待插補信號;

(2)狀態S1:剩余插補脈沖數寄存;

(3)狀態S2:積分累加狀態。

其工作過程為:當沒有啟動信號時,系統繼續保持在空閑狀態IDLE;當有啟動信號start時,系統則從數據緩存器中讀入初始數據,將插補脈沖數寄存在狀態S1中,若插補脈沖數不為零則轉至積分累加狀態S2中,在此狀態中將被積函數寄存器的值與余數寄存器的值進行累加,結果送余數寄存器,若有脈沖溢出,則轉入狀態S1,此時輸出插補脈沖,且狀態S1中剩余脈沖數減“1”;若無脈沖溢出,則狀態S2繼續進行積分累加。最終,狀態S1中的剩余脈沖為零時,返回空閑狀態,插補結束。

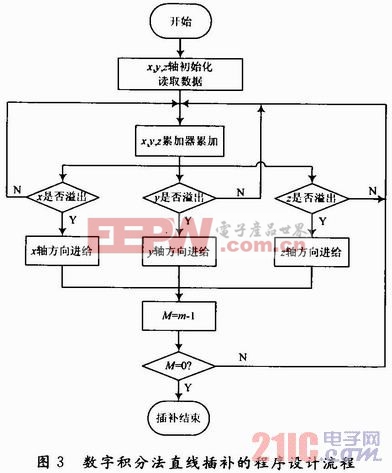

數字積分法直線插補運用硬件描述語言VerilogHDL進行程序編寫的流程圖如圖3所示。

fpga相關文章:fpga是什么

伺服電機相關文章:伺服電機工作原理

評論