基于Virtex 4的雷達(dá)導(dǎo)引頭信號(hào)處理機(jī)的設(shè)計(jì)與實(shí)現(xiàn)

0 引言

本文引用地址:http://www.104case.com/article/190544.htm導(dǎo)彈主要依靠制導(dǎo)系統(tǒng)進(jìn)行制導(dǎo),完成從發(fā)射到命中目標(biāo)的全過(guò)程。制導(dǎo)系統(tǒng)一般利用地面制導(dǎo)雷達(dá)或彈載導(dǎo)引頭對(duì)目標(biāo)進(jìn)行探測(cè)、參數(shù)計(jì)算、控制指令形成與傳輸、程序控制和伺服控制等。雷達(dá)導(dǎo)引頭是建立在雷達(dá)、自動(dòng)控制、制導(dǎo)、微型計(jì)算機(jī)、精密機(jī)械、微電子、小型化和可靠性能多項(xiàng)專門(mén)技術(shù)基礎(chǔ)上的一種復(fù)雜制導(dǎo)設(shè)備。各國(guó)尤其是先進(jìn)國(guó)家都十分重視雷達(dá)導(dǎo)引頭的研制及其相關(guān)技術(shù)的研究,從而將智能化、高命中率、高摧毀概率的導(dǎo)彈武器的研制應(yīng)用推向新階段。

本文采用脈沖多普勒、數(shù)字波束形成等技術(shù),為某型雷達(dá)導(dǎo)引頭信號(hào)項(xiàng)目設(shè)計(jì)了其關(guān)鍵部分——雷達(dá)數(shù)字信號(hào)處理機(jī)。本處理器采用FP GA平臺(tái)實(shí)現(xiàn),文中詳細(xì)介紹了該處理器基于FPGA的基頻信號(hào)產(chǎn)生模塊、回波信號(hào)采集模塊、控制信號(hào)產(chǎn)生模塊和時(shí)鐘模塊等硬件模塊的設(shè)計(jì)思路。

1 系統(tǒng)方案設(shè)計(jì)

目前,主要采用三種方法實(shí)現(xiàn)雷達(dá)數(shù)字信號(hào)處理系統(tǒng)設(shè)計(jì):基于DSP技術(shù)實(shí)現(xiàn)雷達(dá)數(shù)字信號(hào)處理,基于“FPGA+DSP”技術(shù)實(shí)現(xiàn)和基于FPG A技術(shù)來(lái)實(shí)現(xiàn)。本方案選用Xilinx Virtex4 FPGA XC4VSX55,其屬于Xilinx SX系列,專用于高速數(shù)字信號(hào)處理領(lǐng)域,F(xiàn)PGA非常適合于高速數(shù)據(jù)的采集控制、高速數(shù)據(jù)傳輸控制,且目前的主流FPGA均含有硬件乘加器、大量的邏輯單元、流水線處理技術(shù)等硬件結(jié)構(gòu),可高速完成FFT、FIR、復(fù)數(shù)乘加、卷積、三角函數(shù)以及矩陣運(yùn)算等數(shù)字信號(hào)處理。高端FPGA更是含有大量的DSP單元、RAM單元、MGT高速傳輸單元、DDRII數(shù)據(jù)控制器等IP核,這些均是實(shí)現(xiàn)高速實(shí)時(shí)數(shù)字處理的重要資源。此外,F(xiàn)PGA編程靈活,易于升級(jí)。其高度集成性和高靈活性使對(duì)外部硬件的需要更少,額外的硬件開(kāi)銷大大減小,非常適用于雷達(dá)數(shù)字信號(hào)的處理和將來(lái)的算法升級(jí)。因此本方案采用FPGA技術(shù)進(jìn)行雷達(dá)信號(hào)的處理。

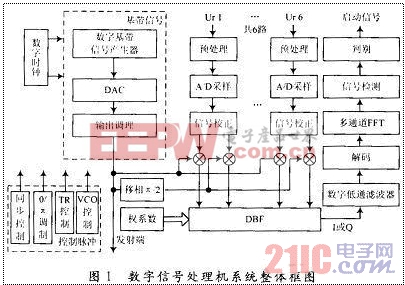

根據(jù)項(xiàng)目的設(shè)計(jì)需求,設(shè)計(jì)的雷達(dá)數(shù)字信號(hào)處理機(jī)系統(tǒng)整體框圖如圖1所示。

輸入調(diào)理電路對(duì)接收到的回波信號(hào)進(jìn)行預(yù)處理,預(yù)處理過(guò)后的信號(hào)經(jīng)ADC轉(zhuǎn)換為數(shù)字信號(hào);采樣后的信號(hào)經(jīng)頻率搬移,將100MHz的中頻信號(hào)搬移到20MHz,然后對(duì)6個(gè)通道的信號(hào)進(jìn)行幅度校正,消除通道間的不平衡問(wèn)題。校正后的6路信號(hào)分別與兩個(gè)正交本振信號(hào)相乘,進(jìn)行數(shù)字混頻,完成信號(hào)的正交分解,得到12路I/Q正交信號(hào)。12路I/Q信號(hào)與預(yù)先設(shè)置的權(quán)值進(jìn)行加權(quán)計(jì)算并進(jìn)行累加,完成數(shù)字波束形成(DBF),得到一路合成信號(hào);通過(guò)FIR低通濾波器,對(duì)數(shù)字波束合成后的信號(hào)進(jìn)行數(shù)字濾波,濾除30 MHz以上的諧波信號(hào);由于發(fā)射信號(hào)采用了偽碼調(diào)相技術(shù),所以對(duì)DBF后的信號(hào)依照發(fā)射信號(hào)的m序列進(jìn)行偽碼解調(diào)(即對(duì)回波信號(hào)進(jìn)行相位變換),完成回波信號(hào)的解碼。對(duì)濾波后的信號(hào)進(jìn)行相參累積,累積次數(shù)達(dá)到設(shè)定值后,進(jìn)行FFT變換;FFT結(jié)果與檢測(cè)門(mén)限進(jìn)行比較,當(dāng)發(fā)現(xiàn)回波信號(hào)特征時(shí),給出回波的通道號(hào)和頻率,并給出啟動(dòng)信號(hào)。

2 系統(tǒng)實(shí)現(xiàn)

2.1 硬件設(shè)計(jì)

結(jié)合系統(tǒng)需求和系統(tǒng)總體設(shè)計(jì),本系統(tǒng)的硬件主要包括A/D采樣部分、D/A輸出部分、控制信號(hào)輸出部分、時(shí)鐘部分、FPGA設(shè)計(jì)及配置、電源管理等六大部分,總體框圖如2圖所示。各功能模塊介紹如下:

(1)A/D采樣部分

根據(jù)性能指標(biāo),系統(tǒng)外接6路模擬信號(hào),信號(hào)頻率為100MHz,輸入信號(hào)幅度為±1 V,幅度分辨率為0.5 mV。因此設(shè)計(jì)了兩片A/D轉(zhuǎn)換模塊ADS6444實(shí)現(xiàn)帶通欠采樣,單片ADS6444支持4通道模/數(shù)轉(zhuǎn)換,最高采樣頻率為105 MHz,采樣位數(shù)為14 b的高性能A/D轉(zhuǎn)換電路,輸入信號(hào)量程為2 VPP,幅度分辨率為0.12 mV。配合前端數(shù)據(jù)調(diào)理芯片THS4513,能滿足系統(tǒng)對(duì)采樣電路的需求。

(2)D/A轉(zhuǎn)換電路

無(wú)論是調(diào)頻連續(xù)波或脈沖多普勒調(diào)制方式,均需要對(duì)外輸出100MHz的基頻信號(hào),因此設(shè)計(jì)了D/A轉(zhuǎn)換電路。D/A轉(zhuǎn)換芯片采用MAX5887,它是14位、500 MSPS數(shù)模轉(zhuǎn)換器(DAC),工作電壓為3.3 V,提供76 dBc的無(wú)雜散動(dòng)態(tài)范圍(SFDR)(fout=30 MHz時(shí))。該DAC支持500MSPS的更新速率,且功耗小于230mW。

(3)控制信號(hào)輸出部分

控制信號(hào)輸出TTL的信號(hào),TTL信號(hào)采用+5 V供電,而數(shù)據(jù)處理芯片F(xiàn)PGA采用的為3.3 V的LVTTL電平,為實(shí)現(xiàn)信號(hào)的正確傳輸,需要信號(hào)轉(zhuǎn)換,因此設(shè)計(jì)了I/O緩沖模塊實(shí)現(xiàn)LVTTL到TTL的信號(hào)轉(zhuǎn)換。I/O緩沖器使用采用美國(guó)TI公司的16位同向緩沖器SN74ALVTHl6245,可以完成LVTTL到TTL的電平轉(zhuǎn)換,最高開(kāi)關(guān)頻率可以達(dá)到80 MHz以上,同時(shí)輸出電流大,可以帶動(dòng)高功耗設(shè)備。

(4)時(shí)鐘部分

數(shù)/模轉(zhuǎn)換部分、模/數(shù)轉(zhuǎn)換部分、FPGA正常工作均需要低抖、高穩(wěn)定性的時(shí)鐘,在此使用專用時(shí)鐘芯片AD9517來(lái)產(chǎn)生系統(tǒng)需要的各個(gè)時(shí)鐘。AD9517是一款集成高頻時(shí)鐘發(fā)生器,具有如下特點(diǎn):低相位噪聲、VCO頻率變化范圍為1.75~2.25 GHz,4路LVPECL時(shí)鐘扇出,輸出頻率范圍為50 MHz~1.6 GHz可調(diào),4路LVDS時(shí)鐘扇出,輸出頻率范圍為25~800 MHz可調(diào),4路LVDS時(shí)鐘扇出可設(shè)置為8路CMOS時(shí)鐘扇出,且相位可調(diào)、可串行控制。

評(píng)論