基于Virtex 4的雷達導引頭信號處理機的設計與實現

(5)FPGA設計

FPGA要完成對A/D采樣數據的數據處理、D/A轉換的數據輸出、控制信號的產生、核心算法的實現、USB調試接口的數據輸入/輸出等,是整個系統設計的重要部分。根據系統需求分析,使用了Xilinx Virtex4SX55。Virtex4 SX55含有512個DSP處理單元,具有強大的數據處理能力,能夠滿足本系統的信號處理需求。

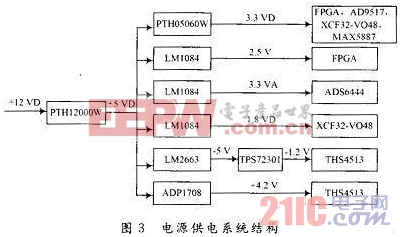

(6)電源管理

本系統采用電源管理模塊將+12 V的外部電源進行穩壓并分成各種幅度的電壓供各個模塊單獨供電,滿足各個模塊對電壓的嚴格需求。其電源供電系統結構如圖3所示。

2.2 軟件設計

本文設計的雷達數字信號處理機的軟件沒汁主要分為FPGA程序設計、系統驅動設計和用戶軟件設計三個部分。FPGA程序是系統算法的核心,完成ADC的控制以及DBF算法等;系統驅動設計和用戶軟件設計主要完成系統的人機交互功能,不是本文討論的重點,此處只討論FPGA程序的設計。

FPGA程序主要完成信號處理算法。該程序利用Xilinx公司提供的System Generator工具,對數字信號處理的過程進行建模和設計。Syst em Generator適于利用FPGA設計高性能數字信號處理系統。它利用業內最先進的FPGA開發高度并行系統提供系統建模和從Simulink與Matlab自動生成代碼的功能,System Generator整合了DSP系統的RTL、嵌入式、IP、Matlab和硬件元件DSP建模。它利用包含信號處理(如FIR濾波器、FFT)、糾錯(如Viterbi解碼器、ReedSolomon編碼器/解碼器)、算法、存儲器(如FIFO,RAM,ROM)及數字邏輯功能的Xilinx模塊集,在Simulink內構建和調試高性能DSP系統。Xilinx模塊集提供的模塊可以使用戶導入Matlab功能(如創建控制電路)及HDL模塊,迅速完成復雜的數字信號處理算法設計。

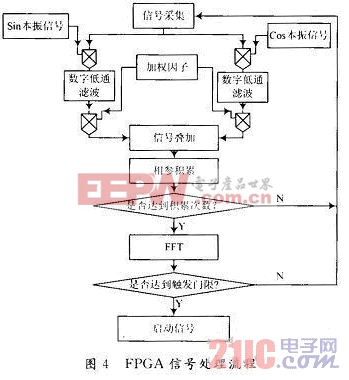

一路回波信號經A/D采集后的數字序列分別與兩個正交本振信號進行相乘,完成正交變換,得到兩路I/Q信號。然后,通過數字低通濾波器實現數字混頻。本設計在這里選擇正弦和余弦兩個信號作為正交變換的本振信號,無論從數學運算上,還是具體實現上都能確保其正交性。設計中采用的是6單元均勻線陣天線,因此共得到12路I/Q信號。12路I/Q信號與加權因子相乘后進行數字波束合成,得到兩路I/Q信號,然后進行信號疊加。疊加后的信號進行相參積累,當積累次數達到設置值時,進行FFT處理;否則,繼續信號采集過程。將FFT處理的結果和設置的門限相比較,如超過門限時,觸動啟動信號;否則,繼續信號采集過程。FPGA處理的流程如圖4所示。

3 系統測試

在實際條件下,對數字信號處理機中的DBF系統合成波束的天線方向圖進行了測試,以檢驗是否和理想條件下的天線方向網一致。具體步驟如下:

(1)測試環境:某研究所暗室。

(2)測試條件:6元15 mm接收天線成均勻直線陣排列、1元發射天線、雷達數字信號處理電路板、轉臺以及其他必要設備。

(3)測試方法:將6元接收天線放置在轉臺的0°刻度所在的直線上,測試的信號源放在轉臺前方,并在90°刻度的延長線上。此時設定陣列天線所在的直線為x軸,法線方向為y軸,轉臺中心為坐標零點。轉動轉臺,使信號源與天線的夾角分別為90°,60°,20°,調整陣列天線權值,使主瓣方向指向信號源方向。調整完成后,測量并記錄三種情況下的天線方向圖。

評論