基于Avalon總線的TFT LCD控制器設計

系統總體設計方案

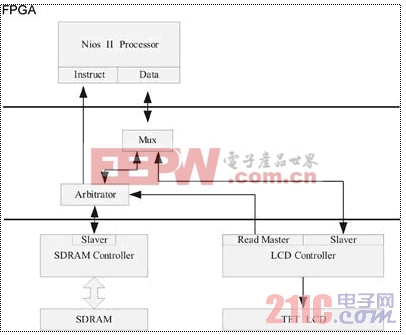

本文引用地址:http://www.104case.com/article/190542.htmNios II處理器在SDRAM中開辟幀緩沖(Frame buffer),可以是單緩沖也可以是雙緩沖。以單緩沖為例。處理器將一幀圖像數據(640×480×2Bytes,RGB565,16bit)存入幀緩沖,然后將幀緩沖的首地址寫入到LCD控制器,并啟動LCD控制器。該控制器自動從傳來的首地址處開始讀取數據,并按照TFT的格式輸出。圖中各模塊由AvalON Bus連接在一起。Avalon Bus是一種簡單的總線結構,Nios II處理器和各種外設都是通過Avalon Bus連接在一起。由圖1可以看出,作為Slaver的SDRAM Controller分別要受到Processor 和LCD Controller的控制,為了解決總線沖突,Avalon Bus自動在有沖突的接口上加入了Arbitrator這樣一個仲裁模塊,用于合理分配總線時間,用戶通過改變每個模塊的權值來改變對其分配總線時間的多少。在這個系統中,SDRAM Controller是影響整個系統性能的關鍵。以SDRAM時鐘頻率為100MHz計算,16bit的SDRAM其數據總帶寬為200MByte/s,640×480×2Bytes×60Hz的TFT LCD要占用36MByte/s左右的帶寬,這對于還要處理其他任務的處理器來說是很大的影響。

本系統的總體設計框圖如圖1所示。

圖1 系統框圖

LCD控制器的FPGA實現

Avalon Bus Slaver從總線接口模塊實現

Avalon從總線接口負責處理器與LCD控制器的接口控制,LCD控制器在整個系統中作為從設備,NIOS II通過該接口對控制寄存器進行設置,控制LCD。

LCD從模塊有四個32bit的可讀寫寄存器,用于控制LCD控制器的工作和指示其工作狀態。

Avalon Bus DMA Master主設備接口模塊實現

Avalon Bus DMA MaSTer負責按照控制模塊的指令,讀取SDRAM中的數據,并寫入到FIFO中,其核心部分是DMA地址累加器。當條件滿足時,地址累加器開始在100MHz的時鐘下以4為單位開始累加用于生成讀取SDRAM的地址。讀完一幀的數據后,自動復位到首地址,繼續累加。

主設備接口采用帶延遲的主設備讀傳輸模式,在這種傳輸模式下,即使沒有接收到上一次的有效數據,主設備也可以發起下一次讀命令。當waitrequest信號無效(低電平)時,主設備可以連續的發起讀命令,當waitrequest信號有效(高電平)時,主設備開始等待,直到其變為低電平。當readdatavalid信號有效(高電平)時,表示讀數據有效,此時主設備可以鎖存數據口上的有效數據。這里沒有使用flush信號,flush信號會清除前面一切未完成的讀命令。Avalon總線保證數據的輸出順序與主設備要求的順序一致(即與主設備地址輸出順序一致)。

readdatavalid信號可以作為FIFO的wrreq信號,這樣可以直接將讀出來的數據寫入到FIFO中。當前地址等于尾地址時,則復位累加器,使之重新開始從首地址累加。地址累加器代碼模塊如圖3。

LCD顯示屏相關文章:lcd顯示屏原理

lcd相關文章:lcd原理

評論