基于FPGA的異步串行總線設計

(1)發射模塊:按照協議向上位機回傳監測數據,發射錯誤重發請求數據等;

(2)接收模塊:接收上位機下傳的參數、命令等;完成起始位的檢測和消息同步,題頭、題尾的對錯判斷,同時將收到的數據進行串并轉換以8bit為單位打入FIFO (First In First Out)中緩存,備譯碼模塊進行命令字譯碼和對下位機控制的信息讀取。

(3)CRC校驗模塊:CRC校驗模塊完成CRC-8編碼功能和CRC-8譯碼功能。當發送消息時,將要發送的數據按8bit打入CRC校驗模塊,對其進行編碼,求出校驗碼并且拼接到題尾后面將其發出;當接收消息時,接收模塊將收到的串行碼按8bit打入CRC校驗模塊,啟動CRC譯碼算法,如果譯碼成功則啟動解消息模塊進行相應的后續工作。如果譯碼失敗,終止本次接收,啟動錯誤重發模塊,要求對放發送上一包消息。

(4)解消息模塊:CRC校驗成功后將啟動解消息模塊進入工作狀態,從FIFO中讀取命令字數據,對命令字進行解碼識別,根據解碼信息肩動其它相應模塊開始工作。

(5)錯誤重發模塊:當接收到串行數據流時,經過題頭、題尾、CRC譯碼判斷,任何一個環節出現錯誤都將終止本次接收流程,同時啟動錯誤重發模塊,發送錯誤重發請求,要求對方重新發送上一包數據。本文引用地址:http://www.104case.com/article/190439.htm

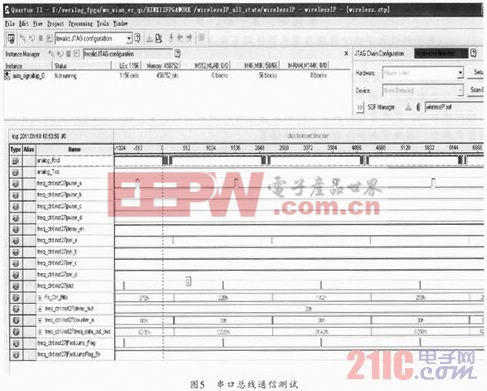

根據圖4所示流程及軟件模塊功能化分,本設計采用Verilog HDL硬件設計語言開發實現。設計靈活,串口速率、編碼模式、傳輸方式等都可根據系統要求從上位機下發參數進行修改。圖5是本串口總線在每秒七萬次的通信頻率狀態下用Quartus軟件中的SignalTAP logic Analy zer抓出的工作時序圖。可以看出串口總線傳輸穩定可靠,完全滿足系統通信的高速傳輸要求。

4 結束語

本文介紹了一種基于FPGA芯片的高速異步串行總線設計。總線協議利用Verilog HDL實現,設計靈活、可讀性強、維護方便、升級移植性能優越、傳輸穩定可靠。隨著通信系統信息吞吐量的日益增加,這種具備多重優點的串行總線設計將被大量使用。

評論