基于FPGA的異步串行總線設計

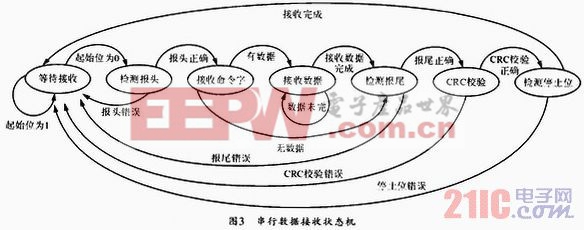

發送消息的過程相對簡單,只需要按照傳輸格式將所要發送的消息進行打包、CRC-8編碼。然后用時鐘將打包好的數據串行打出即可;接收消息相對復雜一些,為了準確接收數據,防止因為時鐘抖動及串行數據傳輸信號衰落而導致的誤碼,接收方要盡可能的靠近每比特數據位的中點進行采樣,所以在設計程序時利用鎖相環將采樣時鐘倍頻到傳輸速率的4倍頻進行同步采樣,這樣采樣點更加接近數據中點,采到的數據更真實串行數據接收狀態機如圖3所示。本文引用地址:http://www.104case.com/article/190439.htm

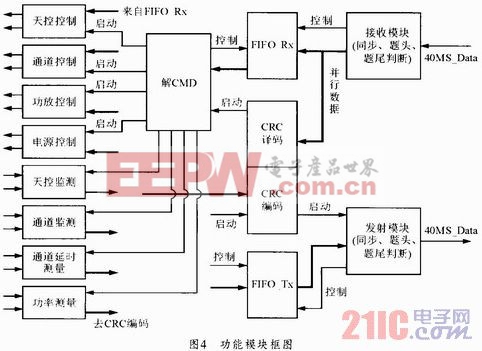

3 功能模塊設計

根據對協議的分析將整個串行總線傳輸協議從功能上劃分為以下幾個饃塊:發射模塊、接收模塊、解消息模塊、CRC校驗模塊、自檢模塊、控制模塊、ID版本存取模塊和錯誤重發模塊等。模塊關系圖如圖4所示。

評論