基于FPGA的數據采集系統設計

3 系統軟件設計

3.1 總體方案設計

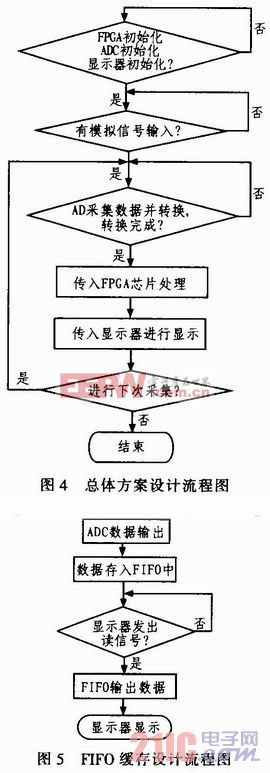

FPGA數據采集系統的軟件總體方案設計流程圖如圖4所示。當FPGA、ADC以及12864顯示器初始化完畢之后,判斷是否有模擬信號輸入到ADC器件中,如果沒有,則等待信號的輸入;如果有,則ADC開始采集數據并轉換。轉換完成之后,送到FPGA芯片進行數據處理。然后,傳送到12864顯示器中進行波形的顯示。最后,再次判斷有無信號輸入到ADC中,如果有,則繼續進行下次的采集流程;如果沒有,則結束程序。

3.2 FIFO緩存設計

由于A/D轉換器、FPGA以及12864顯示器之間處理數據的速度不同,為了消除不必要的數據丟失與毛刺現象或者重復讀取,可以將處理后的數據暫時存入FIFO中。FIFO是一個先入先出的堆棧,利用FPGA內部強大的寄存器功能,設計了一個FIFO的數據緩沖器。

如圖5所示,A/D轉換器將轉換好的數據存入FIFO緩存中,FPGA檢測顯示器12864有無讀信號,如果有讀信號,則FIFO輸出信號給顯示器;如果沒有,則數據繼續存儲在FIFO中,等待被取走。

4 結束語

基于FPGA在高速數據采集方面有單片機和DSP無法比擬的優勢,FPGA具有時鐘頻率高,內部延時小,全部控制邏輯由硬件完成,速度快,效率高,組成形式靈活等特點。因此,本文研究并開發了一個基于FPGA的數據采集系統。本文中所提出的數據采集系統設計方案,就是利用FPGA作為整個數據采集系統的核心來對系統時序和各邏輯模塊進行控制。依靠FPGA強大的功能基礎,以FPGA作為橋梁合理的連接了ADC、顯示器件以及其他外圍電路,最終實現了課題的要求,達到了數據采集的目的。

評論