基于DSP+FPGA的高精度程控交流電源設計

摘要:介紹了一種基于DSP+FPGA芯片技術的高精度程控交流電源的實現方法,利用FPGA實現了任意波形發生功能,并對功率逆變等電路進行了詳細的分析和設計,最后給出了實驗結果以及相關波形。

本文引用地址:http://www.104case.com/article/190356.htm關鍵詞:交流電源;程控;任意波形發生

1 引言

隨著自動測試技術的不斷發展,對程控交流電源的性能也提出了新要求,不僅要求功率大,精度高,而且要求輸出范圍寬,波形可任意程控。這里介紹了一種基于DSP+FPGA芯片技術的高精度程控交流電源的實現方法,利用FPGA實現了任意波形發生功能,并且獲得了極高的輸出精度和靈活的輸出波形控制,滿足各種復雜測試需求。

2 基本原理與方案

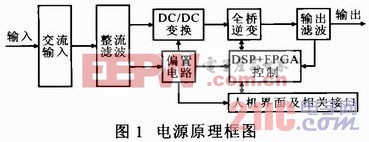

程控交流電源原理框圖如圖1所示。

交流輸入和整流濾波電路將輸入電壓經過整流濾波后為后續電路提供一個較純凈的電壓。偏置電路為所有電路提供偏置電壓。

功率部分結構上采用兩級變換,實現前后級之間隔離,主要包括DC/DC變換和全橋逆變兩部分。由于輸出容量S=750 VA,為減小體積、提高效率,功率變換采用開關方式。考慮到輸出電壓和功率的設計要求,前后級均采用全橋拓撲。前級DC/DC使用高頻變壓器進行輸入與輸出的電氣隔離,同時,控制電路取樣輸出電壓進行閉環控制,可得到穩定的直流輸出。后級全橋逆變采用正弦脈寬調制(SPWM)技術,以任意波形發生器的輸出為參考基準,根據等效面積原理,生成所需波形的等效PWM波。通過控制逆變電路中開關器件的通斷,獲得恒幅值的高頻調制波形,經整形濾波后,得到需要的輸出波形。利用任意波形發生器,改變調制信號的頻率和幅度,可實現輸出的精確調節。

DSP+FPGA控制電路是程控交流電源的核心,它實現了電源高精度實時控制和波形任意發生的需求,完成了功率電路的PID控制和與相關外圍電路的通信。DSP+FPGA控制電路將輸入和反饋的幅值、頻率、相位等信息處理后,生成所需SPWM信號,控制電源輸出,而實際輸出的幅值、頻率等參數在DSP+FPGA控制電路中取樣標定后,送回人機界面及相關接口電路,通過液晶顯示器實現信息實時顯示。

3 關鍵電路設計

3.1 任意波形發生電路設計

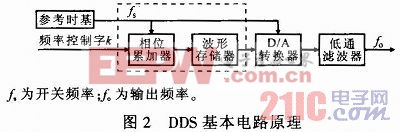

程控交流電源輸出電壓可編程的特性是通過參考電壓信號的可編程特性來實現的。為實現電源任意波形輸出,要求參考電壓信號可以是正弦波(頻率、幅值可根據需要設定),也可以是在正弦波上疊加諧波,還可以是任意變化的動態信號波。可見,產生高精度可編程參考電壓信號的任意波形發生器的設計是程控交流電源設計中的關鍵環節。由于直接數字合成(DDS)技術在相對帶寬、頻率轉換時間、高分辨率、相位連續性、正交輸出以及集成化等一系列性能指標方面遠超過傳統頻率合成技術所能達到的水平,因此采用DDS技術設計任意波形發生器,使輸出具有極高的頻率分辨率和快速輸出轉換能力,同時使用FPGA器件設計DDS電路,可以實現信號波形的多樣化,而且方便可靠,簡單經濟,系統易于擴展。DDS的結構有很多種,其基本電路原理可用圖2來表示。

波形信號的產生由高性能的TMS320C31型DSP控制器實現。該控制器具有強大的指令運算功能和數據處理能力,很容易實現各種控制算法及高速實時采樣,可提高系統的工作效率。DDS電路采用FPGA設計,主要由3部分組成:①k和相位初始控制字A的接收電路,由DSP經鎖存器送

到相位累加器;②相位累加器電路是整個DDS電路的核心,其精度和速度影響整個通道的性能。該電路采用VHDL語言設計。相位累加器接收DSP發送的32位k和A,在時鐘脈沖的作用下,以A為起點,連續進行k值相加,生成有規律的32位相位地址碼,輸出鎖存器將每個相位地址碼鎖存,取其中高18位尋址波形存儲器。在相位舍位條件下,由于相位累加器的輸出為周期序列,易產生有規律的雜散噪聲。為此,采用抖動注入技術,用18位的隨機數與要舍去的低18位相加后,再去尋址波形存儲器,這樣就破壞了尋址序列的周期性,將有規律雜散分量變成隨機的相位噪聲,從而有效消除相位舍位引起的雜散噪聲;③幅度控制字U的接收、D/A轉換和濾波電路。DSP將12位的U送入相應鎖存器,與波形存儲器中的數據一起送入D/A轉換器,經低通濾波器得到所需模擬信號。

(1)頻率可調設計 DDS系統采用5.5 MHz晶振,經128分頻后產生42.968 75 kHz參考時鐘,因此,最小頻率分辨率為42.968 75 kHz/232=10μHz。若要得到45Hz~1kHz步進10μHz的頻率,則k值相應取值為:45Hz時,k=45Hz/10μHz=4.5x106;1kHz時,k=1kHz/10μHz=108。因此,k值取范圍為4.5×106~108。

(2)相位可調設計 相位累加器是32位的,理論上相位分辨率可達到(1/232)x360°=8.38x10-8(°)。為實現相位分辨率為0.1°,則初始相位控制字為0.1/(8.38x10-8)=1193 046。若要依次得到初始相位為0~359.9°,則初始相位值設定為1 193 046的0~3 599倍。將1 193 046以二進制形式存儲于程序存儲器,當接收到相位設定值時,先將設定值乘以1 193 046,再轉換為相位初始控制字。

(3)幅度可調設計 在幅度調節設計中采用了雙D/A的設計方法。波形D/A為DAC1,幅度D/A為DAC2,DAC1用于把波形數據轉換成模擬量,DAC2用于輸出信號的幅度調節。由于DAC1的參考電壓由DAC2提供,因此可利用對DAC1參考電壓的控制來實現幅度的調節。設計中DAC2位數N選用12位,參考電壓UR取5 V。D1為DAC2的輸入數據,D2為DAC1的輸入數據,Uo為D/A轉換器輸出。由此可得:Uo=(URD1/2N)D2/2N。通過查表將數據D2讀到幅度基準寄存器,可獲得幅度范圍0~5 V。經反饋及變換電路后幅度范圍為0~300V。

評論