基于FPGA的數據采集系統設計

摘要:隨著信息技術的飛速發展,各種數據的采集和處理在現代工業控制和科學研究中已成為必不可少的部分。數據采集系統是計算機智能儀器與外界物理世界聯系的橋粱,是獲取信息的重要途徑。以Xilinx公司的Spartan-3系列FPGA芯片XC3S400為核心,采用TI公司的TLC0820型號的A/D轉換器作為模數轉換器件,設計了一個基于FPGA的數據采集系統,并用Verilog HDL語言作為描述語言實現了對TLC0820的采樣控制和FPGA的數據處理等過程的控制,以Xilinx ISE9.1i軟件為平臺,進行了設計輸入、分析與綜合、仿真與驗證等過程仿真實現了這一系統。

本文引用地址:http://www.104case.com/article/190357.htm關鍵詞:數據采集;FPGA;模數轉換;vetilog HDL

常用的數據采集方案往往采用單片機或DSP(數字信號處理器)作為控制器,控制ADC(模數轉換器)、存儲器和其他外圍電路的工作。但由于單片機本身的指令周期以及處理速度的影響,難以達到多通道高速數據采集系統的要求,DSP雖然可以實現較高速的數據采集,但其速度提高的同時,也提高了系統的成本;并且單片機和DSP的各種功能要靠軟件的運行來實現,執行的速度和效率較低,軟件運行時間在整個采樣時間中占很大的比例。而FPGA(現場可編程門陣列)在高速數據采集方面有單片機和DSP無法比擬的優勢,FPGA具有時鐘頻率高,內部延時小,全部控制邏輯由硬件完成,速度快,效率高,組成形式靈活等特點。因此,本文以FPGA作為核心處理器件,進行了數據采集的過程。

1 數據采集系統原理

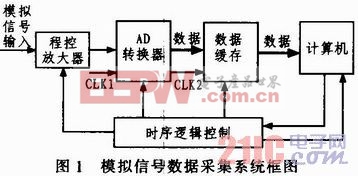

圖1是一個模擬信號的數據采集系統框圖。

由圖可知,系統主要由以下5個部分組成:

第1部分是放大器電路。程控放大器的作用是將傳感器產生微弱的模擬信號進行放大處理。放大器把信號放大到與A/D轉換器滿量程電壓相應的電平值,以便充分利用A/D轉換器的分辨率,放大器的放大倍數可以通過設計放大電路來進行實時控制。

第2部分是A/D模數轉換電路。其功能是將放大后的模擬信號轉換為計算機能夠識別的數字信號。A/D轉換器是采樣通道的核心,所以A/D轉換器是影響數據采集系統采樣速率和精度的主要因素之一。

第3部分是數據緩存電路。A/D轉換后的數據信息一般不能直接傳送到計算機,所以在讀入計算機或其他處理設備之前應該增加數據緩存模塊,這樣能有利于將數據連續的送人計算機。

第4部分是時序邏輯控制電路。它可以控制程控放大器、A/D模數轉換器、數據緩存等單元,并實現與計算機的通信。

第5部分是接口電路。接口電路是數據緩存區的數據傳輸至計算機等設備的紐帶。

2 系統硬件設計

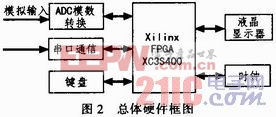

本系統主要研究對模擬信號的數據采集,根據系統的要求與功能的實現,FPGA數據采集系統的總體方案設計結構框圖如圖2所示。

在模擬信號采集的過程中,模擬信號輸入給A/D轉換器,然后經模數轉換之后將8bit的數字信號直接輸出給FPGA進行處理。在FPGA中設計了數據緩沖器FIFO和數據存儲器RAM以及和各級電路對應的的時鐘信號,以保證能夠實時的將ADC轉換過來的數據進行處理。其中,液晶屏可用于顯示被采集的波形,串口通信用于FPGA的在線調試與配置程序的加載,鍵盤用于控制操作。

2.1 數據采集模塊

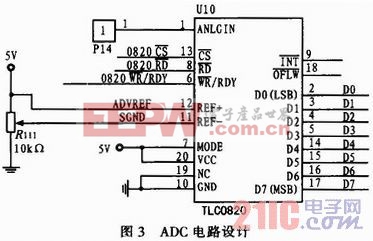

根據本系統對數據采集精度以及速度方面的要求,采用Texas Instruments改進快閃技術的先進的LinCMOS高速8位A/D轉換芯片TLC082 0AC來完成采集過程。它由2個4位快閃轉換器,一個4位數模轉換器,一個加法(誤差)放大器,控制邏輯及一個結果鎖定電路構成。改進的快閃技術可使低功率集成電路在整個溫度范圍內(0~70℃)以1.18 μs(轉換率>1 M)完成8位轉換。該芯片內部采樣和保持電路具有100 ns采樣窗,允許這些器件以高達100 mV/μs的斜升速率轉換連續模擬信號而無須外部采樣器件。TTL兼容的3態輸出驅動器及兩種工作方式允許與不同微處理器接口。單-5 V電源,無須外部時鐘或振蕩器,最大功耗75 mV,兩種工作方式可選。具有差分基準輸入,數據轉化及存取時間為2.5個時鐘周期(MCU晶振選用12 M),最高采樣率20 M。其工作方式連接圖如圖3所示。

2.2 數據處理模塊

FPGA在高速數據采集處理方面有單片機和DSP無法比擬的優勢,FPGA具有時鐘頻率高,內部延時小,全部控制邏輯由硬件完成,速度快,效率高,組成形式靈活等特點。因此我們選擇使用FPGA來進行數據的處理與控制。市場上FPGA的型號與類型非常多,根據本系統的要求,我們這里選擇Xilinx公司生產的Spartan-3系列XC3S400型號的芯片。Spartan-3系列是基于Virtex-II FPGA構架,采用90 nm技術,8層金屬工藝,系統門數超過500萬,內嵌了硬核乘法器和數字時鐘管理模塊。從結構上看,Spartan-3系列將邏輯、存儲器、數學運算、數字處理器、I/O以及系統管理資源完美地集合在一起,使之有更高層次、更廣泛的應用。其主要特性為:采用90 nm工藝,密度高達74880邏輯單元;最高系統時鐘為340 MHz;具有18x18的專用乘法器;核電壓為1.2V,端口電壓為3.3 V、2.5 V、1.2 V,支持24種I/O標準;高達520 kB的分布式RAM和18 972 kB的塊RAM;有片上時鐘管理模塊(DCM);具有嵌入式XtremeDSP功能,每秒可執行3 300億次乘加。

2.3 輸出模塊

輸出模塊主要負責利用液晶顯示器顯示采集到的數據以便進入后續的處理,因此,需要連接有顯示模塊。液晶顯示屏常常采用12864,本系統選用了HS12864_15系列中文圖形液晶模塊,文字圖形可混合顯示且帶有字庫,其特征主要由其控制器ST7920決定,ST7920同時作為控制器和驅動器,它可提供33路com輸出和64路seg輸出。在驅動器ST7921的配合下,最多可以驅動256x32點陣液晶。

評論