基于FPGA的OLED真彩色顯示的設計方案簡述

2 仿真結果

選用Altera 公司Cyclone Ⅲ 系列芯片EP3C10E144C8 為目標芯片,采用Verilog HDL 語言進行設計,在GX - SOPC - EDA - EP3C10 - STARTER -EDK 開發板上進行Modelsim 仿真,仿真結果如圖4 和圖5 所示。

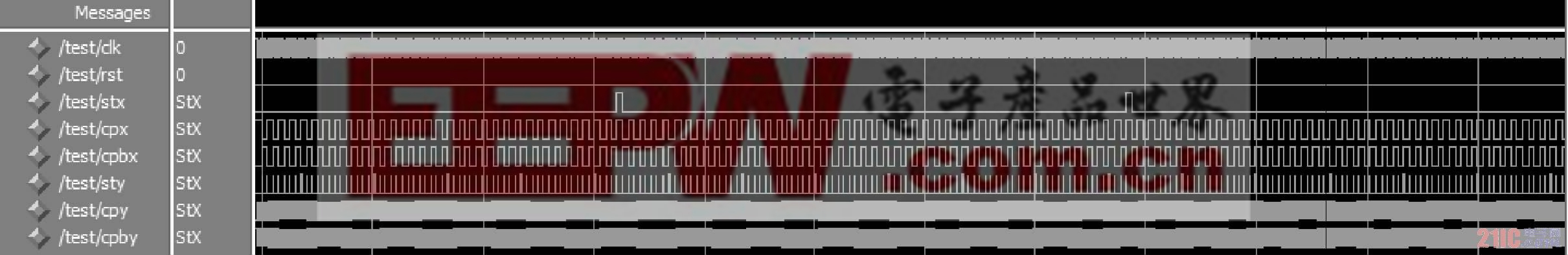

圖4 外圍驅動時序仿真結果

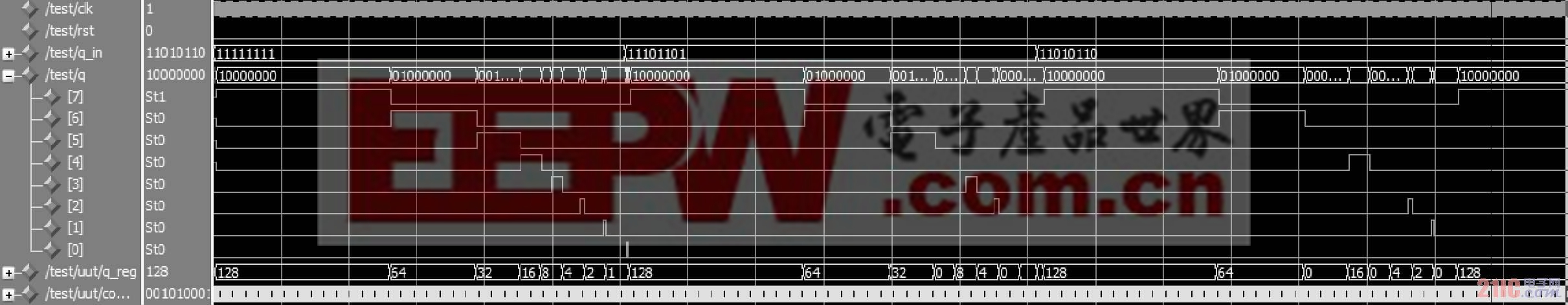

圖5 256灰度產生模擬仿真

由圖4 仿真結果可以看出,80 組列掃描脈沖cpy和cpby 控制80 個Block, 80 個列掃描脈沖完畢后,列掃描起始信號sty 脈沖開始,繼續掃描下一行。90 行掃描完畢后, stx 到來重新選通第一行,依此循環,符合設計的要求。

由圖5 仿真結果可以看出,對于輸入的8 bit 像素數據,經灰度產生模塊轉化為灰度數據。以第一個輸入數據8 hff 為例,每位的顯示時間為128∶ 64∶ 32∶ 16∶ 8∶ 4∶2∶ 1,由其不同組合,從而實現了256 級灰度的功能。

3 結束語

基于FPGA 芯片設計了分辨率為480 × RGB × 640的真彩色OLED 顯示屏的驅動電路,在傳統的子場原理和脈寬調制占空比實現灰度的基礎上,對其進行優化,采用R、G、B 單基色像素分時顯示的方法,實現了256 級灰度功能。經仿真和軟硬件協同仿真驗證,實現了設計所要求滿足的功能。其256 級灰度實現方法簡單靈活,降低了對FPGA 驅動頻率的要求,對于在高刷率、高分辨率、高灰階顯示器件上的應用,具有很高的實用價值。利用該電路系統可以實現OLED 顯示的全彩色實時動態圖像的傳輸,為今后OLED 作為大尺寸顯示器提供了技術支持。

評論