基于FPGA的OLED真彩色顯示的設計方案簡述

數字驅動電路的困難在于工作頻率比模擬驅動電路高得多,現階段較為實用的灰度調制方法主要有兩種。一種是脈寬調制法,即對驅動脈沖實現占空比的控制; 另一種方法是子場控制法,這種方法將發光時間按1∶ 2∶ 4∶ 8∶ …劃分為若干個子場,不同的子場導通組合,就能實現不同的灰度等級。但采用脈寬調制法,其時序復雜,要求顯示屏有較高響應速度; 而采用子場法要求驅動頻率較高,對高灰度級的實現難度大。

考慮到幀頻與OLED 屏體顯示效率的折中,使驅動電路工作頻率在一個合理水平,在脈寬調制和子場原理的基礎上,對這兩種方法進行優化,256 級灰度采用通過對圖像數據按位分時顯示的方法實現,即對輸入的8 bit 像素信號RGB,通過給每種顏色字節的不同位分配不同的顯示時間達到灰度顯示的目的,使每位的顯示時間為128∶ 64∶ 32∶ 16∶ 8∶ 4∶ 2∶ 1,利用其組合可以得到256 級灰度顯示所對應的子像素發光時間,實現視覺上的256 級灰度即1 667 萬色顯示,以實現高質量的顯示畫面。

為實現256 級灰度,將一個像素點的掃描時間分成19 個單位時間t,8 bit 灰度數據q[7: 0]從高位到低位所占的時間分別為8t,4t,2 t,t,t,t,t,t.為使不同位顯示時間成一定比例,從q[3]開始引入t /2 的消影時間,q[2]引入t /4 的消影時間,d[1]引入t /8 的消影時間,d[0]引入t /16 的消影時間,如圖2 所示,由控制電路產生消隱信號進行消隱。由此計算OLED 屏亮度百分比λ = ( 8 + 4 + 2 + l + 1 /2 + 1 /4 + 1 /8 + 1 /16 ) /19 = 83. 9%.

1. 3 FPGA 控制器

利用FPGA 的處理速度和數據寬度高的優勢以及芯片中可利用的豐富資源,為分辨率為480 × RGB ×640 的OLED 顯示屏設計了外圍驅動控制電路。其主要作用是向OLED 顯示屏提供掃描控制信號及進行OLED 顯示數據的數字信號處理。

根據OLED 顯示屏周邊接口的結構和特性,利用FPGA 芯片為其設計外圍的驅動控制系統,為OLED 屏提供控制信號以及傳輸所要顯示的數據信號。

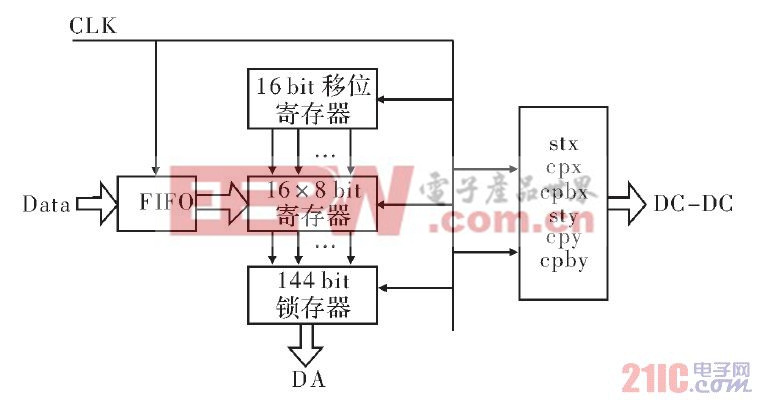

如圖3 所示,經解碼后的圖像數據存入FIFO( First In First Out) 緩存中,在主時鐘的控制下,FIFO中的圖像數據將被載入到一個16 × 8 的數據裝載寄存器,當這16 個8 位數據裝載寄存器裝滿時,將被一個144 位的鎖存器鎖存,等待進入D/A 轉換模塊; 同時FPGA 控制器還將在主時鐘的控制下產生行列移位時鐘和行列掃描起始脈沖,產生的時鐘和脈沖進入DC -DC 轉換模塊。

圖3 FPGA 控制器結構框圖。

1. 4 各種控制信號周期及頻率

為使FPGA 控制器能工作于一個合理的驅動頻率以及提高顯示屏的亮度,在結構上采用標準單元塊的形式。對于分辨率480 × 3 × 640 的顯示屏,以8 × 16個顯示像素燈管構成一個單元塊,將480 × 3 行分組組合成為90 個塊( Block) ,即每塊由一組列信號同時驅動16 行像素。設計列掃描驅動電路時,將640 列電極分組組合成為80 個塊( Block) ,每個塊并行驅動8 列像素。

OLED 顯示屏的刷新頻率是60 Hz /s,即顯示一幀圖像的時間為1 /60 s,設為T,所以,行掃描起始信號stx 的周期T 為16 667 μs,占空比為1∶ 90; 因為OLED顯示屏480 × 3 行電極分組組合成為90 個Block,所以每一塊的選通時間為T /90,即185. 185 μs.而cpx 和cpbx 是一對反相不交疊的脈沖信號,占空比為50%,在脈沖信號的高電平和低電平時,都有一個Block 行像素被選通,即在cpx 和cpbx 一個周期內有兩個Block 行像素被選通,所以行掃描驅動脈沖cpx 和cpbx的周期為T /45,即370. 370 μs.

同理,OLED 顯示屏的列被分為80 個Block,每個列Block 的選通時間為2. 315 μs,列掃描起始信號sty的周期為185. 185 μs,占空比為1 ∶ 80.列驅動脈沖cpy 和cpby 亦是一對反相不交疊的脈沖信號,占空比為50%,在脈沖信號的高電平和低電平時,都有一個Block 被選通。由于每個列Block 的選通時間為2. 315 μs,所以列掃描驅動脈沖cpy 和cpby 的周期為4. 630 μs.

在每個列Block 選通期間,從FIFO 中并行讀出的8 個8 bit 數據進入數據鎖存器鎖存。在每個BLOCK選通期間都將進行一次數據的鎖存,所以數據鎖存信號Lock 的周期為2. 315 μs.因為當16 個8 位的數據裝載寄存器都載滿數據的時候才進行這144 個數據的鎖存,所以16 位移位寄存器時鐘clk _reg 的周期為0. 145 μs.從FIFO 中讀出數據的速度必須和向數據裝載寄存器中裝載數據的速度一致,則FIFO 的讀時鐘clk _ fifo 的周期也為0. 145 μs.對0. 15 μs( 6. 896 MHz) 進行近似為7 MHz,所以令系統的基本時鐘為14 MHz,由FPGA 外部晶振產生。讀時鐘為基本時鐘的二分頻。

1. 5 FPGA 工作流程

FPGA 處理器是設計的核心部分,其工作流程為,在每個clk_fifo 時鐘周期下,從8 個FIFO 緩存中并行讀出8 個8 bit 像素數據,在時鐘clk_reg 上升沿到來時, 16 位移位寄存器發生移位,它的輸出端接16 個8位數據裝載寄存器的片選端,這樣16 個8 位數據裝載寄存器逐個被選通,此時這些數據就可以載入到16 個8 位數據裝載寄存器中,這16 個8 位寄存器的輸出端接在144 位鎖存器的輸入端上。16 個時鐘clk_reg 上升沿過后, 16 個8 位數據裝載寄存器都將依次被裝載滿,此時數據鎖存信號Lock 到達,將144 個數據鎖存到144 位數據鎖存器中,然后這些數據進入到DA 轉換模塊,轉換成16 路模擬量,送至OLED 顯示屏,完成一個Block 數據的載入。

在列掃描驅動脈沖cpy 和cpby 的控制下,80 個Block 依次被選通,在每一Block 被選通期間,都將進行一次144 個數據的移位寄存和鎖存,當80 個Block都鎖存完之后,一行數據的載入也就完成了。當第一行的80 個Block 數據顯示完畢后,列掃描起始信號sty過來,又開始從第一列掃描,與此同時,在行掃描驅動脈沖cpx 和cpbx 的作用下,第二行像素被選通,所以,這時將進行第二行的1 到80 個Block 的數據載入,以此類推,直到90 行數據都顯示完畢之后,行掃描起始信號stx 到來,重新選通第一行,循環往復,一幀幀地顯示數據。

評論