基于FPGA實(shí)現(xiàn)固定倍率的圖像縮放

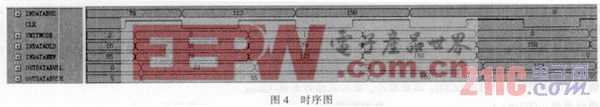

基于FPGA實(shí)現(xiàn)的仿真時序圖如圖4所示。本文引用地址:http://www.104case.com/article/190182.htm

在本例中時鐘為輸入的點(diǎn)時鐘,為了在X3像素周期時輸出2個像素:Y2和Y3,采用了擴(kuò)充數(shù)據(jù)總線的方式。

2.2.2 基于FPGA實(shí)現(xiàn)列方向的卷積

數(shù)據(jù)流在行方向放大后寫入雙口RAM,然后從另一側(cè)端口讀出進(jìn)行列方向的放大。由于行方向的卷積算法,雙口RAM中至少應(yīng)存儲連續(xù)的3行輸入圖像像素數(shù)據(jù),其中2行輸入圖像像素數(shù)據(jù)處于被讀出狀態(tài),產(chǎn)生放大后的輸出圖像像素,另一行空間被寫入當(dāng)前的輸入圖像像素數(shù)據(jù),循環(huán)刷新。

列方向的單元體和行方向相同,也由3個輸入像素和4個輸出像素組成,每種狀態(tài)下也是同樣的卷積系數(shù),只是圖像橫向的空間變換成圖像豎向的空間,因此基于FPGA實(shí)現(xiàn)列方向的卷積的方法與基于FPGA實(shí)現(xiàn)行方向的卷積的方法相同,此處不再贅述。

3 結(jié)束語

基于FPGA實(shí)現(xiàn)圖像縮放,需要根據(jù)圖像縮放的倍率確定包含適當(dāng)數(shù)量像素的單元體。在單元體內(nèi)部,根據(jù)圖像縮放算法確定每個輸出像素的計(jì)算公式和卷積系數(shù),確定實(shí)現(xiàn)點(diǎn)時鐘倍頻效果的硬件方案。順向映射方式輸入和輸出處于幀同步狀態(tài),由于輸出像素數(shù)量多于輸入像素,輸出像素的點(diǎn)時鐘頻率要高于輸入像素。本文行方向的放大過程,點(diǎn)時鐘頻率平均增加1/3倍,列方向的放大過程,點(diǎn)時鐘頻率還要繼續(xù)增加1/3倍。實(shí)現(xiàn)倍頻效果可以采用更高頻的獨(dú)立時鐘,或者倍頻輸入點(diǎn)時鐘,再或者增加數(shù)據(jù)總線寬度。為節(jié)省數(shù)據(jù)存儲空間,當(dāng)對圖像放大時,先進(jìn)行列方向的放大,后進(jìn)行行方向的放大;當(dāng)對圖像縮小時,先進(jìn)行行方向的縮小,后進(jìn)行列方向的縮小。

基于FPGA實(shí)現(xiàn)圖像縮放功能實(shí)時性強(qiáng)、分瓣率高。許多航空電子嵌入式圖像處理系統(tǒng)是由固定的視頻源和顯示設(shè)備組成,系統(tǒng)中圖像縮放的倍率是固定的。本文基于FPGA硬件實(shí)現(xiàn)固定倍率的圖像縮放,能夠大幅度降低設(shè)計(jì)難度,減少工作量。

基于FPGA硬件實(shí)現(xiàn)固定倍率的圖像縮放的方法已經(jīng)應(yīng)用于某款航空電子產(chǎn)品中,電路板的原有硬件沒有變動,對電路板中FPGA重新進(jìn)行了設(shè)計(jì),增加了新的內(nèi)容,應(yīng)用效果良好。

評論