基于FPGA實現固定倍率的圖像縮放

F(x,y)的值可以對其鄰域的原始圖像進行二維卷積運算得到。

其中mxn為鄰域范圍,f(i,j)是輸入原始圖像,s(i,j)為系數函數。

因為圖像中鄰近的像素存在著相關性,所以輸出圖像像素可以依據其在原始輸入圖像映射位置鄰域的像素數據卷積得到。鄰域范圍內各個像素的相關度由系數函數決定,鄰域的范圍決定了算法的運算速度。

基于FPGA硬件實現固定倍率的圖像縮放,為了降低FPGA設計的復雜性,提高圖像縮放算法的運算速度,增強系統的實時性,將2維卷積運算分解成2次1維卷積運算,對輸入原始圖像像素先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。

2 圖像縮放的FPGA實現

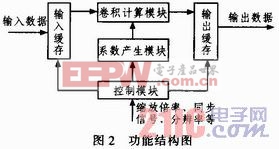

2.1 基于FPGA實現圖像縮放的功能結構

基于FPGA實現圖像縮放的功能結構圖如圖2所示。本文引用地址:http://www.104case.com/article/190182.htm

卷積計算模塊的硬件結構由算法決定,每個點時鐘周期內,對輸入原始圖像像素和系數先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。系數產生功能是依據控制模塊確定的狀態,產生算法要求的系數。輸入緩存由控制模塊不斷刷新,保證每一時鐘輸入給卷積計算模塊相應的像素數據。輸出緩存提供下一環節數據流接口。

控制模塊是核心邏輯部分,可以采用逆向映射方式(按照輸出像素的時間順序遞增,選擇對應的輸入像素得到結果),也可以采用順向映射方式(直接在輸入像素的時序中產生輸出像素)。

逆向映射方式工作在輸出圖像的時鐘域,控制模塊根據縮放倍率、分辨率和同步信號,確定輸入像素坐標的增量大小,使得在每一時鐘周期輸入緩存中出現相應的像素數據。因為逆向映射方式需要使輸出時鐘域與輸入時鐘域保持同步,所以需要大容量的輸入數據存儲空間,才能確保在每個時鐘周期提供相應的輸入像素數據。順向映射方式輸入和輸出像素有很強的時序對應關系,按照輸入像素的時序進程實時確定輸出像素的時序,輸出圖像分辨率發生變化,但幀頻一致。圖像縮放過程中,輸入一個像素可能會輸出2個或3個像素,控制模塊可以采用輸出緩存、雙口RAM、變換時鐘域、增加數據總線寬度等方法達到這種同步。順向映射方式符合輸入圖像的時序,不需要大容量的數據存儲空間,具體根據圖像縮放算法的鄰域大小而定。

2.2 基于FPGA實現圖像縮放的方法

基于FPGA實現圖像縮放時,無論是逆向映射方式還是順向映射方式,控制模塊的設計都比較復雜。為了發揮FPGA的優勢,大幅度降低設計難度,簡化硬件結構,文中把圖像縮放過程設計為一個單元體的循環過程,在單元體內部,可以事先計算出卷積系數。例如,把每行720個像素,放大到768個像素,相當于每輸入15個像素,輸出16個像素。此時可以把15個像素作為一個單元體,事先計算出每個輸入像素周期的卷積系數,在FPGA中設計一個包含15種情況的狀態機即可。單元體的像素數量越少,事先計算卷積系數和狀態機設計的工作量就越少,因此像素的數量控制在20個以內,必要時可以采用近似的整數比。當輸出像素的數量與實際要求相差很小時,圖像邊緣部分增加或減少幾個像素對顯示效果影響甚微,因此各種圖像縮放倍率情況下,相應個數的輸入像素都可以作為一個合適的單元體。

為論述方便,文中以將768x576的輸入圖像放大到1 024x768為例,說明基于FPGA實現對輸入原始圖像像素先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。

評論