基于FPGA實現固定倍率的圖像縮放

摘要:基于FPGA硬件實現固定倍率的圖像縮放,將2維卷積運算分解成2次1維卷積運算,對輸入原始圖像像素先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。把圖像縮放過程設計為一個單元體的循環過程,在單元體內部,事先計算出卷積系數。降低了FPGA設計的復雜性,提高了圖像縮放算法的運算速度,增強了系統的實時性,已經應用于某款航空電子產品中,應用效果良好。

關鍵詞:FPGA;圖像縮放;卷積運算;單元體

航空電子圖像處理系統為操作者提供各種圖像及字符信息,隨著傳感器、顯示器的性能指標不斷提升,圖像處理系統的設計面臨越來越大的挑戰,其中圖像縮放的功能是圖像處理系統的關鍵技術要求。圖像縮放功能有兩種實現方案:1)軟件實現,其優點是算法選擇靈活多樣,生成的畫面質量較高,缺點是運算時間長。2)硬件實現,其優點是分辨率高,實時性強,缺點是不易實現功能強大的優秀算法。

近年來,FPGA技術發展迅速,片內集成了PLL、硬件乘法器、存儲器,具有了實現優秀算法的充足資源。許多航空電子嵌入式圖像處理系統是由固定的視頻源和顯示設備組成,系統中圖像縮放的倍率是固定的。文中針對此展開重點研究,基于FPGA硬件,實現固定倍率的圖像縮放。

1 圖像縮放的算法

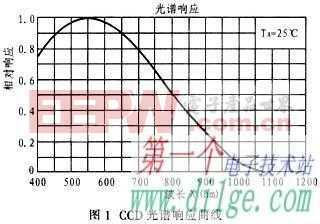

數字圖像的縮放是一個處理2維離散信號的過程。輸出圖像中任一個像素F(x,y),均可以在輸入圖像f(x,y)的像素矩陣中找到其對應的位置,如圖1所示。

評論