基于FPGA的腦機接口系統方案

光標控制模塊描述光標的圖形,控制光標的移動。通過改變光標的坐標和分頻來控制光標移動的方向和速度。光標的顏色為紅色。

基于FPGA的VGA視覺刺激器充分利用了FPGA半定制電路的特點,采用同步時序設計方式,不但性能穩定,而且能根據需要靈活地設計不同的視覺刺激器。它實現方便,功能強大,兼具用硬件或軟件方式實現視覺刺激器的優點。

1.3 瞬態視覺誘發電位的提取與識別

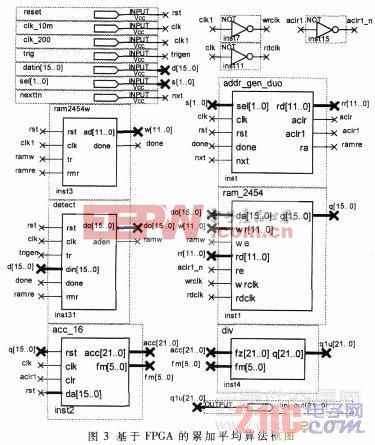

累加平均方法是最經典的誘發電位信號處理方法,也是電生理測量中提高信噪比最常用的方法[2]。在FPGA中設計的累加平均算法的框圖如圖3所示,包括觸發信號檢測模塊、RAM地址控制模塊、異步雙口RAM、累加器和除法器。

觸發信號檢測保證了刺激與視覺誘發電位的鎖時同步關系。只有檢測到最早閃爍的刺激模塊的觸發信號,才把腦電數據存儲到RAM中。當達到要求的閃爍次數時,停止數據的寫入。根據刺激模塊之間的延時關系,可以確定與各個刺激模塊相應的數據在RAM中的起始地址。然后,按照起始地址讀出數據給累加器,累加的次數與閃爍次數相同。最后,用除法器除以累加的次數,得到累加后的平均結果.

知識產權(IP)核,是指己驗證的、可重利用的、具有某種確定功能的IC模塊。FPGA有大量各種用途的IP核。這些IP核對內核進行了參數化,通過頭文件或圖形用戶接口(GUI)可以方便地對參數進行操作。通過異步雙口RAM IP核調用片內RAM來緩存腦電數據,保證了數據接口的同步和數據處理速度。用累加器IP核和除法器IP核來實現算法中的累加器和除法器。

只采用累加平均的方法, 需要進行上百次才能得到可靠的誘發電位波形, 信號提取的時間太長。在少量次累加平均時,為了進一步提高信噪比,提取出較為理想的誘發電位波形,采用數字濾波的方法來減少噪聲的影響。FIR濾波器具有嚴格的線性相位,穩定性好,而且通頻帶比較平坦。所以,采用FIR濾波器來實現數字濾波。用窗函數設計法設計一個15階的低通FIR濾波器,窗函數為海明窗,截止頻率為10 Hz。利用MATLAB工具箱中的FDATool設計濾波器,并轉換為HDL代碼,可以很方便地在FPGA中實現FIR濾波器。通過調用CycloneⅡ芯片中用于DSP運算的嵌入式乘法器來實現FIR濾波中的乘法運算。與基于邏輯單元的乘法器相比,嵌入式乘法器性能更高,占用邏輯單元更少。嵌入式乘法器能夠與CycloneⅡ器件的M4K RAM塊進行無縫集成,實現高效的DSP算法[6]。

瞬態視覺誘發電位的識別,就是要將誘發電位信號轉換成一系列控制命令,從而實現人腦與外界的通信與控制。模板匹配是傳統的模式識別方法之一。相關系數是變量之間相關程度的指標,可以用于判斷曲線擬合程度。用相關系數來衡量模板與未知模式匹配的好壞,是一個有效且可行的方法。

首先,選定一個特征明顯的瞬態視覺誘發電位波形,作為模板匹配的參考模板;然后,把實時提取誘發電位波形與參考模板做相關系數計算。若相關系數值大于設定的閾值時,就認為檢測到了的誘發電位,發出控制命令,使光標移向相應的刺激模塊,從而實現瞬態視覺誘發電位的識別。

相關系數的計算公式如下:

假定模板的數據為y,可以先離線計算出公式(1)中含y項的值,存在ROM中,從而提高實時計算的速度。只需要1個乘加器IP核,調用FPGA芯片中的嵌入式乘法器,就可以實現分子和分母中的乘加運算,節省了器件的資源。用開根號IP核來實現開根號運算。

FPGA運行速度快,內部程序并行運行,并且有DSP運算IP核和嵌入式乘法器,能夠快速準確地完成腦電處理算法,滿足信號處理的實時性要求。

評論