在便攜式應用中,利用零功耗CPLD來降低系統總成本

3. 通用I/O引腳擴展

I/O是 input/output的縮寫,即輸入輸出端口。每個設備都會有一個專用的I/O地址,用來處理自己的輸入輸出信息。CPU與外部設備、存儲器的連接和數據交換都需要通過接口設備來實現,前者被稱為I/O接口,而后者則被稱為存儲器接口。存儲器通常在CPU的同步控制下工作,接口電路比較簡單;而I/O設備品種繁多,其相應的接口電路也各不相同,因此,習慣上說到接口只是指I/O接口。

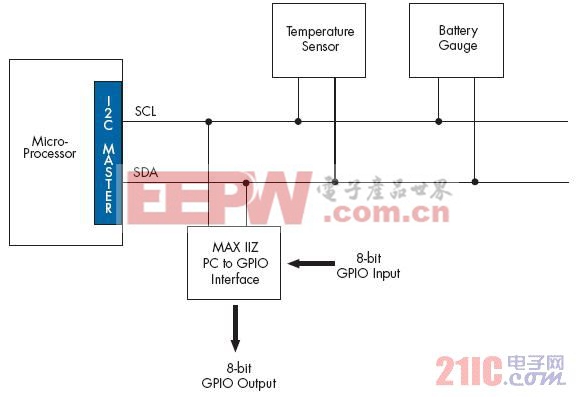

在很多情況下,CPLD是微控制器、ASSP和ASIC優異的輔助器件。例如,在一個常見的通用I/O(GPIO)引腳擴展應用中,設計人員可以把小型低成本微控制器的可編程能力和CPLD的GPIO資源結合起來。CPLD構建一組內部寄存器,微控制器通過I2C或SPI等串口來訪問這些寄存器(圖3),這使得微控制器能夠利用現有的串口來擴展其I/O總數。CPLD擴展I/O也可以用于實現電壓轉換,從而提高了CPLD的實用性。

圖3:GPIO引腳擴展。

雖然上述例子采用的是微控制器,但同樣也適用于采用ASSP和ASIC的情況。例如,很多設計人員發現用小規模ASIC通過串口來驅動CPLD這種方案的成本要比具有相同I/O能力的大規模ASIC方案低得多。

過去,人們認為“可編程邏輯”并不意味著“低功耗”。不過,零功耗CPLD的出現改變了這一觀點,這一技術使得低功耗電子產品設計人員能夠充分利用可編程邏輯的諸多優勢。現在,除了具備CPLD在一般應用中已得到認可的杰出性能外,零功耗CPLD還能夠降低便攜式產品的總功耗。

4. 接口橋接

橋接(Bridging),是指依據OSI網絡模型的鏈路層的地址,對網絡數據包進行轉發的過程。 是工作在osi的第二層的。一般的交換機,網橋就有橋接作用。就交換機來說,本身有一個端口與mac的映射表,通過這些,隔離了沖突域(collision)。 簡單的說就是通過網橋可以把兩個不同的物理局域網連接起來,是一種在鏈路層實現局域網互連的存儲轉發設備。網橋從一個局域網接收MAC幀,拆封、校對、校驗之后 ,按另一個局域網的格式重新組裝,發往它的物理層。

便攜式應用設計人員經常需要連接具有不同I/O接口的器件。這一功能被稱為橋接,因為CPLD被用來構成不同接口之間的“橋”。圖4所示為采用CPLD來橋接兩種不同的串口:I2C和SPI。該設計可以在Altera MAX IIZ EPM240Z CPLD中實現,使用約43%的可用邏輯和6個I/O引腳。

圖4:利用MAX IIZ CPLD橋接I2C與SPI。

圖5所示為一個主處理器與SPI主機的接口,這是一個利用CPLD來實現串并轉換接口的實例。這個例子創建了一個主處理器總線接口和一個完整的SPI主機,可以在MAX IIZ EPM240Z CPLD中實現,占用約30%的可用邏輯和25個I/O引腳。

在圖6中,CPLD被用于橋接兩種不同的并口。這一設計實例實現了PXA310主處理器總線與Compact FLASH+器件的接口,可采用MAX IIZ EPM240Z CPLD實現,使用約17%的可用邏輯及59個I/O引腳。

6.降低功耗的應用

上述應用展示了利用低功耗CPLD來實現便攜式應用中的多種常見功能。下一組應用將介紹利用零功耗CPLD的獨特功能來降低便攜式應用功耗的途徑。

圖5:利用MAX IIZ CPLD實現主處理器至SPI接口。

評論