基于FPGA的可復用通信接口設計

3.2.3. 頂層TOP模塊

本文在分析協議的基礎上建立了高速可復用SPI總線的基本結構,包括時鐘生成模塊,數據傳輸模塊, 并用上層TOP模塊調用底層的兩個模塊。頂層模塊的重要作用就是讓分模塊能夠順利的運作起來。所以此 SPI核的頂層模塊要寫入控制字,通過狀態機控制調用時鐘生成模塊和數據傳輸模塊正常運行。其經ISE綜 合后如圖4所示。

圖4.頂層TOP模塊電路

4、仿真與驗證

仿真與驗證是IP核設計中非常重要的一部分,因為它直接關系著IP的可用性。將用verilog 描述好的SPI 接口電路用ISE進行綜合,然后用modelsim 軟件進行仿真[5]。在建立測試平臺時,首先要建立模擬Wishbone 協議的master模塊,同時建立模擬SPI協議的slave模塊,再將接收/發送數據和地址進行比較、校驗。因此 Spi-top Testbench總體架構可分為:Wishbone master model、SPI master core、SPI slave model 三個模塊。

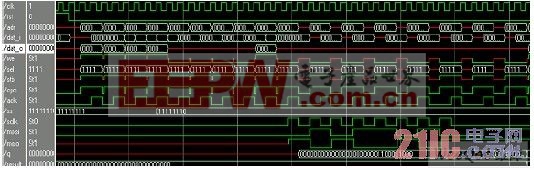

為了簡單仿真8bit數據傳輸,首先進行復位,然后設置寄存器,再進行寄存器校驗,無誤之后進行8bit 數據傳輸,在tx上升沿發送數據,rx下降沿接收數據,仿真波形如圖5所示。同理可以仿真64bit、128bit等 數據傳輸仿真波形。

圖5. 8bit數據傳輸仿真波形

用ISE軟件進行編譯,將生成的網表文件通過JTAG下載到xilinx 公司的spartan3 系列FPGA運行,在ISE 的輔助分析下得到了正確的結果。

5、結束語

隨著半導體技術的進步,FPGA 的價格越來越便宜, 工作頻率越來越高,使用FPGA 實現SPI 通信 接口是切實可行的。

本文作者創新點:設計過程中很多變量都采用參數形式,具體應用于工程實踐時根據實際需要更改參 數即可,充分體現了可復用性。由于SPI對傳輸時序要求非常嚴格,所以本文工作中設計了一種比較可靠, 穩定的時鐘生成模塊,它對于奇偶分頻的情況分別考慮,從而避免了以往SPI總線中對系統時鐘奇分頻時 會出現分頻出的時鐘不穩定的問題。數據傳輸模塊采用較簡潔的并串互轉結構,一次最多可傳輸128位, 速度是遵守SPI協議的同類器件里較快的。并且從128位到8位可選具體一次要傳輸多少位,有別于以往一 次傳輸的位數為定值的情況。

評論