基于FPGA的可復用通信接口設計

3、設計原理

Verilog HDL 是一種硬件描述語言,他可以用來進行各種級別的邏輯設計,可以用來進行數字邏輯系統 的仿真驗證、時序分析和邏輯綜合等,應用十分廣泛。本文使用Verilog設計 SPI接口模塊,實現可IP復用 的通用結構。根據SPI總線原理,可用幾個功能模塊來實現微處理器與從設備之間的雙向數據傳輸。

3.1. 系統架構設計

根據SPI 總線的原理,本設計的SPI Master同SPI協議兼容,在主機側的設計相當于wishbone總線[2]規 范兼容的slave設備,總體架構可分為以下3個功能模塊[3]:Clock generator、Serial interface、Wishbone interface

3.2. 模塊設計

3.2.1 .時鐘產生模塊spi-clgen設計

SPI時鐘分頻模塊中的時鐘信號的來源是外部系統提供的時鐘clk_in,模塊會根據各個不同接口的時鐘 分頻因子寄存器,產生相應的時鐘輸出信號clk_out。由于SPI沒有應答機制,為了能夠保證時序的可靠性, 特別設計了一個無論對于奇分頻還是偶分頻都異常可靠的時鐘生成模塊產生傳輸所需要的串行時鐘。

此模塊重點考慮了奇分頻的情況,為了節省資源對奇分頻的做改動同時也能實現偶分頻的情況。對輸入主 時鐘的同步奇整數分頻,可以簡單地用一個Moore機來實現,編碼采用Moore機增加了可靠性。

master核系統輸入時鐘clk-in通過divider分頻產生clk-out,通過改變divider的值,可以實現任意分頻的時鐘 輸出[4]。其頻率表達式如下:

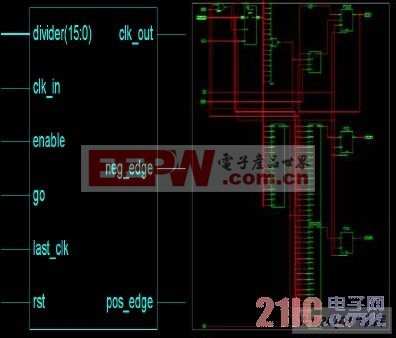

用verilog語言描述時鐘產生模塊,用ISE綜合后,其生成電路如圖2所示。

圖2.時鐘產生模塊電路

3.2.2. 串行接口模塊spi-shift設計

數據傳輸模塊是SPI的核心模塊。此模塊負責把并行進來的數據串行傳出,串行進來的數據并行傳出。 本文設計的shift與通常的SPI移位模塊設計不同,原因在于這里考慮了寄存器的復用,以使用較少硬件資源 來增大一次傳輸數據的位數,從而提高數據傳輸的整體速率。對于并行進來的數據位寬比較長,比如128 位的數據時,為了提高傳輸的速度,本文設計工作中犧牲了資源改進了以前的保守的SPI模塊。SPI MaSTer 核在主機側作為slave設備接收數據,同時作為master設備發送數據。此模塊verilog代碼經ISE綜合后如圖3 所示。

圖3.串行接口模塊電路

評論