基于FPGA嵌入式系統的雷達信號模擬器設計

1.4 實測數據的信號重構

國內在雷達數據采集方面的研究日趨成熟,基于PCI、USB接口的數據采集系統都能滿足雷達中視頻采樣的要求,而且可以根據需要將采集的數據存盤或軟件實時回放處理[5-7]。本系統解決的問題是將系統采集到的數據或磁盤陣列上存儲的其他系統采集到的雷達實測數據通過模擬系統重構出雷達回波信號,做到真實環境的可重復再現,為雷達接收系統性能的檢測提供了有利條件。信號重構過程需要知道雷達回波采樣時的采樣率,保證模擬系統DA信號輸出的速率與數據采集時的采樣速率一致,避免采集和恢復速率的不匹配造成雷達信號的非線性失真。同時實測數據幀的組成形式必須是已知的,這樣才能提取雷達信號的同步、方位、仰角等信息,將對應的幅度信息與方位、仰角同步。

2 具體實現

2.1 硬件設計

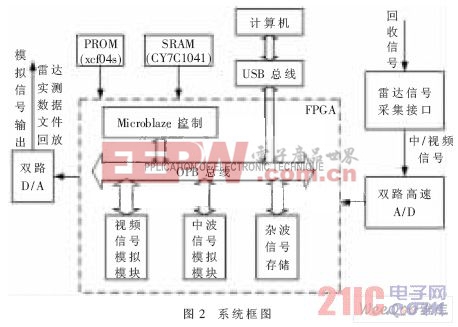

FPGA采用的是Xilinx公司的100萬門FPGA芯片XC3S1000,其配置芯片為Xilinx公司的4 MB容量PROM芯片XCF04S,以主動串行方式對FPGA進行上電配置。AD、DA分別為ADI公司12位105 MS/s高速模/數轉換芯片AD9432與14位105 MS/s高速數/模轉換芯片AD9764。SRAM采用Cypress公司的256k×16 bit SRA。

M芯片CY7C1041用于對數據進行大容量緩存,以滿足USB的傳輸需要。USB控制器選用Cypress公司的EZ-USB FX2系列USB2.0芯片CY7C68013,封裝為PQFP128。它支持USB2.0高速傳送,最高速率可達480 Mb/s。系統框圖如圖2所示。

2.2 FPGA程序設計

FPGA程序主要包括雷達信號模擬模塊、雷達信號采集與傳輸控制模塊和SDK中Microblaze的控制與參數傳遞模塊。雷達信號模擬模塊主要完成對雷達中頻/視頻和雜波信號的模擬,為雷達的接收系統和信號采集模塊提供自檢測試信號。雷達信號采集與傳輸控制模塊主要完成對雷達中頻/視頻信號的采集與傳輸控制,該模塊為系統真實回波的模擬提供了實測數據。參數的傳遞主要由兩部分組成:上位機的信號參數輸入或信號模擬系統自帶的鍵盤掃描輸入與Microblaze核之間的參數傳遞;Microblaze將對應的輸入參數通過中斷調用的形式傳遞給信號或雜波產生模塊。在ISE 9.1環境下通過VHDL硬件語言產生脈沖、LFM等信號,利用EDK 9.1的附件將在ISE 9.1中產生的信號模塊轉化為對應的IP核[8]。在EDK開發中,可以將在ISE中產生的信號模擬的IP核直接添加到工程中,IP核和Microblaze處理器之間通過OPB總線實現信號參數和中斷信號的傳遞,使整個開發過程模塊化。基于FPGA的嵌入式系統設計的EDK開發中有硬件模塊設計和軟件控制2個部分,使整個系統兼容了FPGA并行處理的高速率和軟件編程的簡潔。

2.3 驅動程序設計與使用

FX2的設備驅動程序有2種:一種用來在設備接入時從主機下載固件到RAM中,稱為固件下載驅動程序(wdgtldr.sys);另一種是在設備重新列舉后加載的通用設備驅動程序(ezusb.sys),應用軟件通過該設備驅動程序與FX2通信[9]。

固件下載驅動程序(wdgtldr.sys)是利用CyprESS公司提供的固件下載驅動程序源代碼和用戶編譯成功的固件代碼,在Win2000 DDK中創建的。在將固件代碼下載到RAM中后,系統清除內存中的固件下載驅動程序,并進行重新列舉,讓8051固件控制FX2。此時,系統獲得由8051固件提供的新的ID號,認為有新的USB設備接入,并據此加載相應的通用設備驅動程序。通用設備驅動程序一般不需要重新編寫,可以直接使用Cypress公司已經編好的驅動程序ezusb.sys。

評論