基于FPGA嵌入式系統的雷達信號模擬器設計

摘 要: 結合FPGA嵌入式系統具有硬件電路高并行度和軟件編程控制簡單的特點,設計了一套基于FPGA嵌入式系統的雷達信號模擬器,能夠完成雷達中頻和視頻信號、雜波和干擾信號的模擬,實現雷達系統在不具備實際接收前端的情況下對雷達后級的調試,信號產生和時序控制功能均在嵌入微處理的FPGA中完成,外圍電路簡單,具有很好的工程實用價值。

本文引用地址:http://www.104case.com/article/189985.htm在現代雷達系統的研制和調試過程中,對雷達性能和指標的測試是一個重要環節,在這個環節中,利用模擬目標信號的方式與外場實測相比具有花費少、可重復和靈活性高的優勢。實際的雷達在接受目標回波時,回波中的雜波和噪聲是很大的,甚至有些時候可以淹沒目標回波信號。但是,在人為地對雷達進行測試時,有時只對雷達的某個和某些參數感興趣,希望在回波中表征感興趣的參數強一些,這時就應該在回波中去掉雜波和噪聲的影響,而這在實際的外場試飛過程中是不可能實現的,這也是雷達信號模擬器對場外試飛的一大優勢。

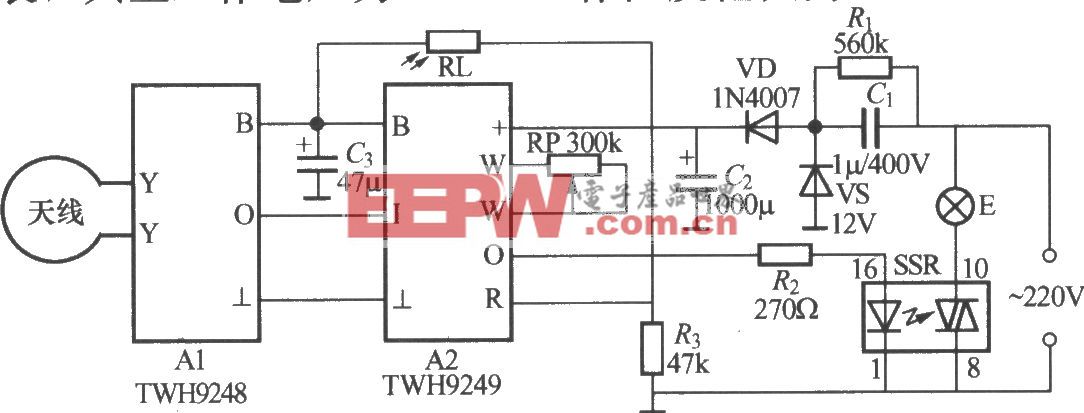

FPGA作為高性能數字信號處理系統中的關鍵部件,在雷達信號模擬和雷達信號采集等方面有著巨大的開發潛能,采用這些技術對雷達系統和環境進行模擬,可重復性高,可以多次模擬同一情況下雷達的性能,便于分析。目前對雷達信號模擬器的研究比較多,通用的方式是軟硬件相結合,使系統既有很大靈活性又可以滿足信號實時輸出的要求。以往的設計中FPGA一般用來控制整個系統的時序,本設計采用集成微處理器的FPGA,同時完成信號模擬和時序控制的功能,改變了以往信號處理DSP+FPGA中FPGA作為協處理器的模式[1-3]。整個設計僅需要具有嵌入內核的FPGA和簡單的外圍電路,使系統的集成度更高,由于FPGA在信號處理中并行處理的優勢,系統實時性強。系統采用工業標準的總線結構以及模塊化設計,具有良好的通用性、兼容性以及可擴充性。

1 系統組成

1.1 雷達信號的模擬

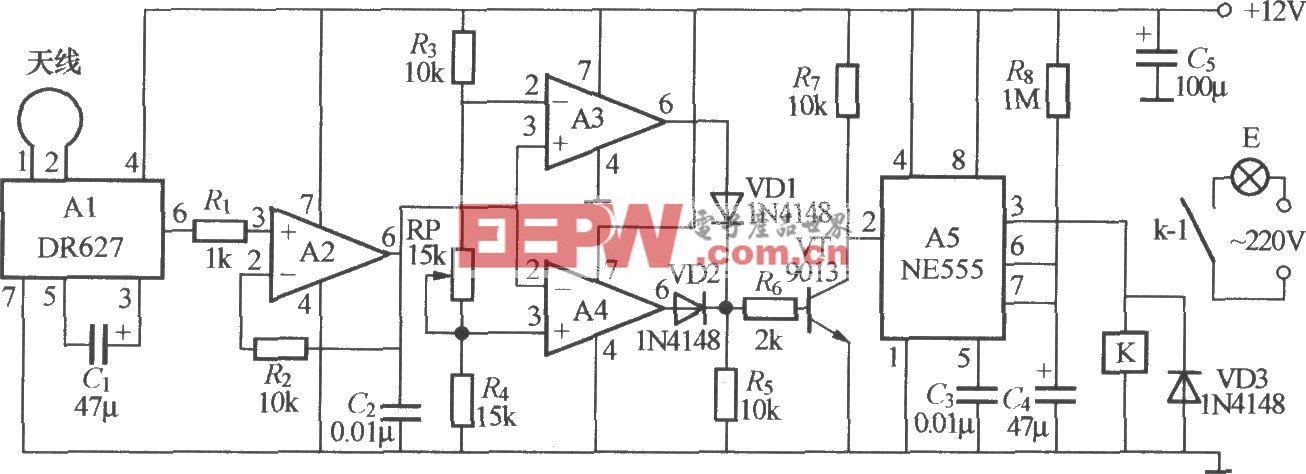

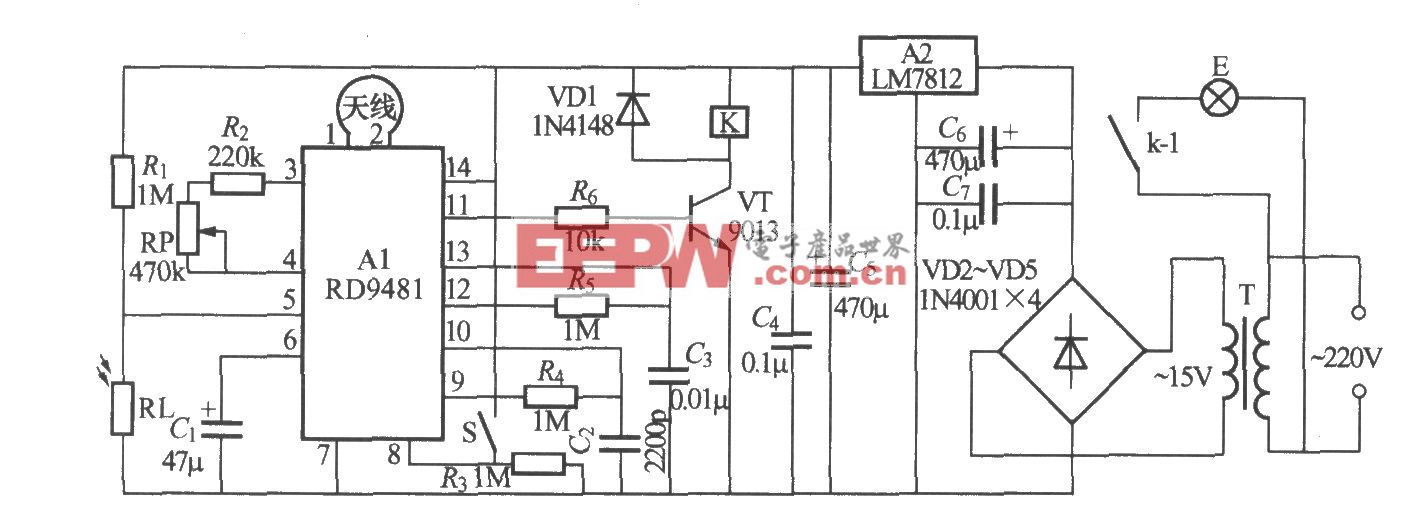

雷達信號模擬模塊(如圖1)主要完成對雷達中頻和視頻模擬。其中中頻信號模擬可以模擬產生雷達中頻線性調頻脈沖信號,視頻信號模擬可以模擬一路非相參視頻信號或兩路相參視頻信號。雷達信號模擬模塊內部包括:天線控制、觸發控制、波門控制以及信號產生等子模塊。天線控制模塊根據天線參數產生天線掃描信號;觸發控制模塊根據觸發信號參數產生周期性的觸發脈沖信號;波門控制模塊根據天線掃描信號、觸發脈沖信號以及目標方位、仰角和距離參數在指定方位、仰角和距離上選通波門輸出目標信號,信號產生模塊根據參數設置產生對應幅度。

1.2 雜波的模擬

雜波是雷達回波的重要組成部分,只有對雜波有效的建模,并將其疊加在目標信號上,才能使模擬出的雷達回波更接近真實情況。通常該模型用統計隨機過程來描述。雜波的模擬有2種途徑:(1)利用Matlab在電腦上產生。首先根據雷達環境和被測雷達參數,選擇合適的雜波模型以及統計特征參數,建立雜波數據庫;然后在計算機中利用零記憶非線性變換法產生雜波隨機序列[4]。目前最常用的雜波幅度分布模型有韋布爾模型、對數正態模型和K分布模型,設計中產生表示雷達雜波幅度的N個數據樣本Z1,Z2,…ZN,這些樣本具有上述某種給定的概率分布和任意給定的功率譜,將這些隨機樣本序列在磁盤上保存下來。PC機上實現隨機序列,具有幅度分布和頻譜特性可選擇的優點。(2)利用線性反饋移位寄存器(LFSR)產生隨機的數字噪聲。LFSR可以被視為一個線性移位寄存器組,并且每個寄存器的輸入都是它前一個寄存器輸出的一個線性函數。在FPGA中設計一個16 bit隨機數字噪聲模擬模塊,此序列發生器的初始值為0XFFFF,數字噪聲信號的周期為216-1=65 535。基于硬件實現的隨機序列,具有循環周期長、隨機性好、資源消耗少的優點。

在實時模擬時,基于雷達天線波束與雜波區域幾何關系,用戶可以根據情況選擇使用哪種方法產生隨機序列,通過硬件和軟件系統直接模擬雷達的雜波回波信號。

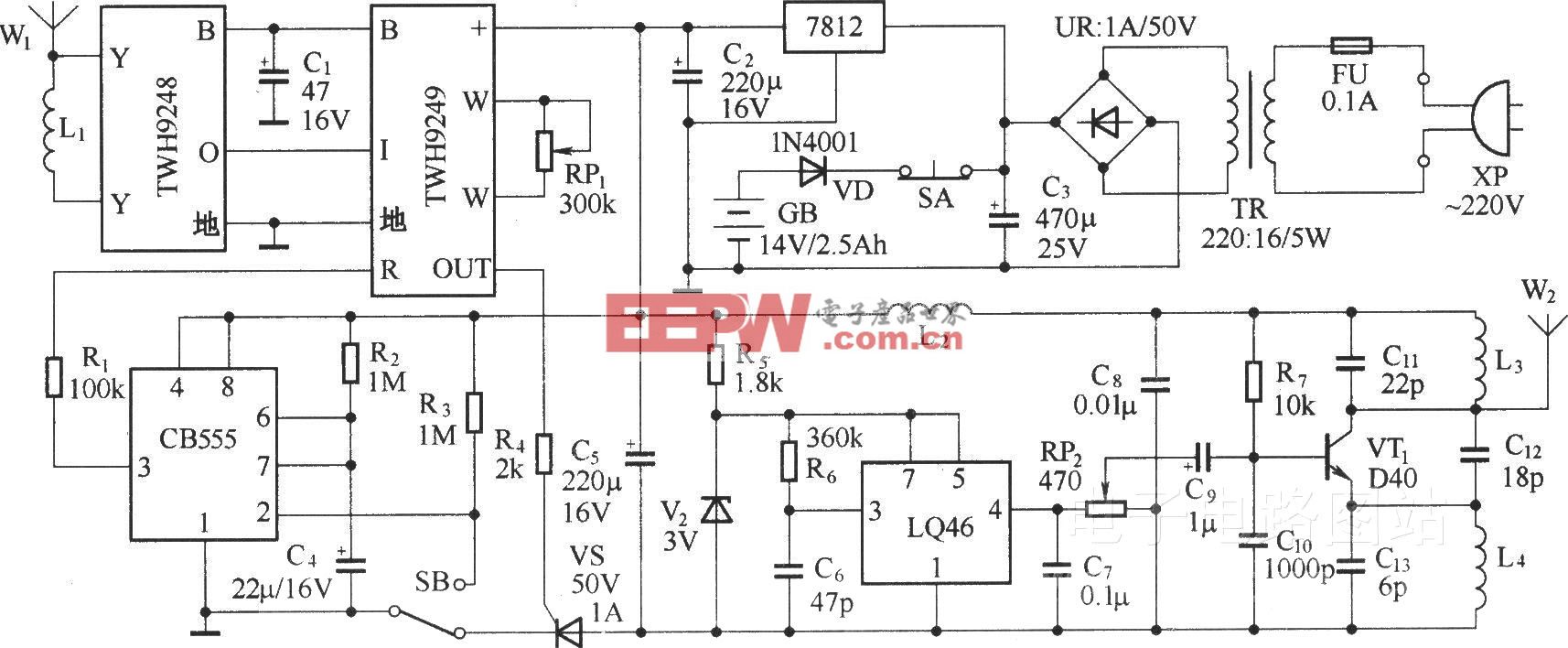

1.3 干擾信號的模擬

雷達干擾信號的模擬能夠模擬真實戰場環境下的一些干擾信號,包括噪聲干擾以及欺騙性干擾,從而可實現對雷達抗干擾性能的檢測。噪聲干擾包括多普勒噪聲干擾、瞄準式噪聲干擾、調頻噪聲干擾;欺騙干擾包括距離欺騙、速度欺騙、假目標等。

噪聲干擾信號的形式比較復雜,主要是通過上位機產生對應的數據,以文本的形式存儲下來。在配置FPGA時,將文本文件作為ROM的初始化文件,在編程過程中以查表的形式生成噪聲干擾信號。

對脈沖雷達距離信息的欺騙主要是通過對收到的雷達照射信號進行延時調制和放大轉發來實現。由于單純的距離質心干擾造成的距離誤差較小(小于雷達的距離分辨單元),所以對脈沖雷達距離信息的欺騙主要采用距離假目標干擾和距離波門拖引干擾。距離假目標干擾的模擬在FPGA中體現出來的就是2組重復頻率不同的脈沖串,2組脈沖串之間的時間差就對應著延時調制,可以通過計數器控制2個脈沖之間的延遲調制。波門拖引干擾時,通過FPGA控制脈沖寬度和對應的功率水平,最終將目標回波脈沖分為2個脈沖,且假目標的功率水平比真實目標的功率水平要高。

評論