Verilog HDL語言在FPGA/CPLD開發(fā)中的應用

由上述這個程序可以看出:Verilog HDL程序是由模塊構成的。每個模塊的內容都是嵌在module和endmodule兩個語句之間實現(xiàn)特定的功能的。每個模塊都由兩部分組成,一部分描述接口;另一部分描述邏輯功能,即定義輸入是如何影響輸出的。如程序中的sequdet(x,z,clk,rst)就是模塊的端口,聲明了模塊的輸入、輸出口。接下來就是模塊中最重要的部分邏輯功能的定義。在模塊中產生邏輯,Verilog HDL語言有3種方法:

(1)用“assign”聲明語句。這種方法很簡單,只需寫一個“assign”,后面再加一個方程式即可。這也是最常用的方法之一。如程序中的assign z==(state==D x==1)?1:0;就表示狀態(tài)為D時又收到了1,表明收到“01101”應使Z輸出為高電平。

(2)用“always”塊。它常被用來描述時序邏輯,上面的程序中即用這個模塊完成了狀態(tài)機的狀態(tài)轉化功能。

(3)采用實例元件的方法。這時只要鍵入元件的名字和相連的引腳即可。這樣就可以用上面這不長的程序,完成這個對序列的檢測功能,并且邏輯描述也十分容易理解。

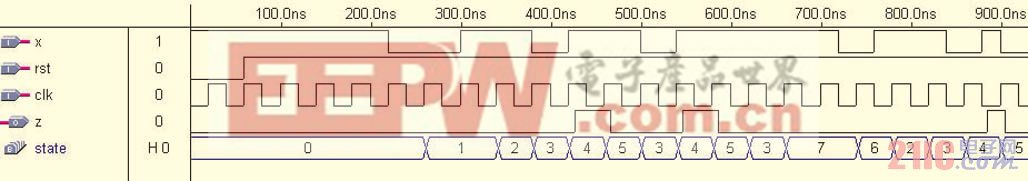

上述程序輸入完成后,接下來首先要經(jīng)EDA設計軟件進行編譯。本設計采用的是美國ALTERA公司的MAX+PLUSII軟件,經(jīng)Compiler編譯器編譯,沒有任何問題后。建網(wǎng)表、邏輯綜合、適配、劃分、時域分析、裝配等均已自動完成,并生成多個后續(xù)工作要用的文件。編譯成功表明已為所設計的項目建立了一個編程文件,但還不能說明該文件在各種情況下都有正確的響應,因此編譯通過后還要進行功能和時序仿真,仿真結果如圖2所示。

經(jīng)仿真發(fā)現(xiàn)輸出Z和輸入X有一段延時。通過波形很難給出定量的信號延時關系,為此我們在進行定時分析。定時分析結果如圖3所示,從表中顯示出了“CLK”到“Z”的延遲路徑為7.6ns、“X”到“Z”的延遲路徑為6ns。這樣,經(jīng)Verilog HDL語言的文本編輯、編譯、仿真波形編輯、仿真和定時分析一系列設計步驟,設計出符合要求的數(shù)字系統(tǒng)后就可以通過編程器下載到指定的芯片中去。

綜上所述,則更能體會到Verilog HDL語言的優(yōu)勢:由于它在其門級描述的底層,也就是晶體管開關的描述方面比VHDL等各種其它的HDL語言有更強的功能。所以在復雜數(shù)字邏輯電路和系統(tǒng)的設計仿真時更有優(yōu)勢;描述的設計思想、電路結構和邏輯關系清晰明了,并且設計語言簡練、易學易用;其模塊化分層結構在大規(guī)模設計時更能體現(xiàn)出優(yōu)勢。因此可以看出,Verilog HDL語言在EDA設計中相對與其他的各種硬件描述語言更有優(yōu)勢。

3 結束語

隨著集成電路規(guī)模的越來越大,數(shù)字系統(tǒng)設計的越來越復雜,Verilog HDL語言在硬件電路設計的優(yōu)越性也會越來越顯突出。目前,數(shù)百萬門規(guī)模的FPGA/CPLD已進入實用,Verilog HDL強大的系統(tǒng)描述能力、規(guī)范的設計結構和簡潔、靈活的編程風格會使其必將能會用來完成大數(shù)字系統(tǒng)、超大規(guī)模數(shù)字系統(tǒng)的幾乎全部設計任務。

評論