Verilog HDL語言在FPGA/CPLD開發(fā)中的應(yīng)用

1 引言

本文引用地址:http://www.104case.com/article/189865.htm近30年來,由于微電子學(xué)和計(jì)算機(jī)科學(xué)的迅速發(fā)展,給EDA(電子設(shè)計(jì)自動(dòng)化)行業(yè)帶來了巨大的變化。特別是進(jìn)入20世紀(jì)90年代后,電子系統(tǒng)已經(jīng)從電路板級(jí)系統(tǒng)集成發(fā)展成為包括ASIC、FPGA和嵌入系統(tǒng)的多種模式。可以說EDA產(chǎn)業(yè)已經(jīng)成為電子信息類產(chǎn)品的支柱產(chǎn)業(yè)。EDA之所以能蓬勃發(fā)展的關(guān)鍵因素之一就是采用了硬件描述語言(HDL)描述電路系統(tǒng)。就FPGA和CPLD開發(fā)而言,比較流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL和Verilog HDL因適合標(biāo)準(zhǔn)化的發(fā)展方向而最終成為IEEE標(biāo)準(zhǔn)。但與VHDL相比,Verilog HDL有個(gè)最大的優(yōu)點(diǎn):它是一種非常容易掌握的硬件描述語言,只要有C語言的編程基礎(chǔ),一般經(jīng)過2~3個(gè)月的認(rèn)真學(xué)習(xí)和實(shí)際操作就能掌握這種設(shè)計(jì)技術(shù)。并且完成同一功能Verilog HDL的程序條數(shù)一般僅為VHDL的1/3。而VHDL設(shè)計(jì)技術(shù)則不很直觀,需要有EDA編程基礎(chǔ),通常需要有多余半年的專業(yè)培訓(xùn)才能掌握這們技術(shù)。可見,用Verilog HDL語言有更高的優(yōu)越性。

2 設(shè)計(jì)實(shí)例

通常設(shè)計(jì)數(shù)字電路大都采用自頂向下將系統(tǒng)按功能逐層分割的層次化設(shè)計(jì)方法,這比傳統(tǒng)自下向上的EDA設(shè)計(jì)方法有更明顯的優(yōu)勢(shì)(當(dāng)時(shí)的主要設(shè)計(jì)文件是電路圖)。因?yàn)橛勺皂斚蛳碌脑O(shè)計(jì)過程可以看出,從總體行為設(shè)計(jì)開始到最終邏輯綜合,形成網(wǎng)絡(luò)表為止。每一步都要進(jìn)行仿真檢查,這樣有利于盡早發(fā)現(xiàn)系統(tǒng)設(shè)計(jì)中存在的問題,從而可以大大縮短系統(tǒng)硬件的設(shè)計(jì)周期。這也是HDL語言設(shè)計(jì)系統(tǒng)硬件的最突出的優(yōu)點(diǎn)之一。并且在頂層設(shè)計(jì)中,要對(duì)內(nèi)部各功能塊的連接關(guān)系和對(duì)外的接口關(guān)系進(jìn)行描述。而功能塊實(shí)際的邏輯功能和具體的實(shí)現(xiàn)形式則由下一層模塊來描述。在系統(tǒng)的底層設(shè)計(jì)中,由于其對(duì)系統(tǒng)很強(qiáng)的行為描述能力,可以不必使系統(tǒng)層層細(xì)化,從而避開具體的器件結(jié)構(gòu),從邏輯行為上直接對(duì)模塊進(jìn)行描述和設(shè)計(jì),隨后EDA設(shè)計(jì)軟件或相應(yīng)的第三方工具軟件中的綜合器將程序自動(dòng)綜合成為具體FPGA/CPLD等目標(biāo)芯片的網(wǎng)表文件,這種避開具體器件結(jié)構(gòu)的方式也是它的重要優(yōu)勢(shì)之一。

下面以序列檢測(cè)器的設(shè)計(jì)為例具體說明。

序列檢測(cè)器是時(shí)序數(shù)字電路中非常常見的設(shè)計(jì)之一。它的主要功能是:將一個(gè)指定的序列從數(shù)字碼流中識(shí)別出來。接下來就以設(shè)計(jì)“01101”這個(gè)序列的檢測(cè)器為例,說明Verilog HDL語言的具體應(yīng)用。設(shè)X為數(shù)字碼流輸入,Z為檢出標(biāo)記輸出,高電平表示“發(fā)現(xiàn)指定序列”,低電平表示“沒有發(fā)現(xiàn)指定的序列”。設(shè)輸入的碼流為“001101101111011111...”,則其序列檢測(cè)器的邏輯功能如表1所示。

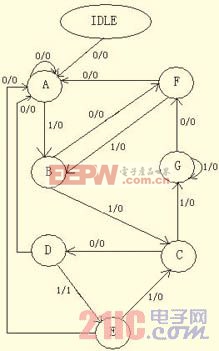

在時(shí)鐘2~6中,碼流X里出現(xiàn)指定序列“01101”,對(duì)應(yīng)輸出Z在第6個(gè)時(shí)鐘變?yōu)楦唠娖?ldquo;1”,表示發(fā)現(xiàn)指定序列“01101”,Z輸出“1”。同理在第9個(gè)時(shí)鐘對(duì)應(yīng)輸出Z也為“1”。根據(jù)這個(gè)邏輯功能描述,我們可以分析得出狀態(tài)轉(zhuǎn)換圖(見圖1)。

其中狀態(tài)A~E表示5位序列“01101”按順序正確地出現(xiàn)在碼流中。因?yàn)檩斎氪a流X是隨機(jī)的,因此可能會(huì)有很多重疊的情況發(fā)生。這樣在轉(zhuǎn)換圖中相應(yīng)的還要有狀態(tài)F和G。設(shè)初始狀態(tài)為IDLE,則有相應(yīng)的Verilog HDL語言程序如下。

module seqdet(x,z,clk,rst);

input x,clk,rst;

output z;

reg[2:0] state;

wire z;

parameter IDLE=3'd0,

A=3'd1,

B=3'd2,

C=3'd3,

D=3'd4,

E=3'd5,

F=3'd6,

G=3'd7;

assign z=(state==D x==1)?1:0;

always@(posedge clk or negedge rst)

if(!rst)

begin

state=IDLE;

end

else

casex(state)

IDLE:if(x==0)

state=A;

else state=IDLE;

A:if(x==1)

state=B;

else state=A;

B:if(x==1)

state=C;

else state=F;

C:if(x==0)

state=D;

else state=G;

D:if(x==1)

state=E;

else state=A;

E:if(x==1)

state=C;

else state=A;

F:if(x==0)

state=A;

else state=B;

G:if(x==0)

state=F;

else state=G;

default: state=IDLE;

endcase

endmodule

評(píng)論