針對(duì)FPGA內(nèi)缺陷成團(tuán)的電路可靠性設(shè)計(jì)研究

參數(shù)u反映了IC 內(nèi)部缺陷成團(tuán)性的強(qiáng)弱,稱(chēng)為模型的成團(tuán)因子。u 越大,缺陷成團(tuán)性越弱;u 越小,缺陷成團(tuán)性越強(qiáng)。

進(jìn)一步分析表達(dá)式(5)、(6),對(duì)于任意的u>0 ,由于

所以有

。

缺陷成團(tuán)時(shí)片內(nèi)冗余容錯(cuò)電路的無(wú)故障概率和失效率比缺陷均勻分布時(shí)的都要高。缺陷成團(tuán)性增大了冗余容錯(cuò)電路的失效率,削弱了冗余容錯(cuò)的可靠性增長(zhǎng)功效。

多項(xiàng)式

,其值隨參數(shù)u增大而增大,因此失效率Qn隨參數(shù)u增大而減小,并且在u=0時(shí)取得最大值。成團(tuán)因子u越大,冗余容錯(cuò)電路的失效率越低、可靠性就越高。這一結(jié)論對(duì)冗余容錯(cuò)電路可靠性設(shè)計(jì)具有重要指導(dǎo)意義。

成團(tuán)因子

缺陷成團(tuán)性強(qiáng)弱可以理解為缺陷相關(guān)性的強(qiáng)弱。缺陷成團(tuán)性越強(qiáng),缺陷相關(guān)性就越強(qiáng),成團(tuán)因子越小,反之亦然。若應(yīng)用式(4)分析一個(gè)冗余容錯(cuò)電路,則成團(tuán)因子反映的是冗余容錯(cuò)電。路內(nèi)缺陷的平均相關(guān)度缺陷團(tuán)面積是個(gè)隨機(jī)值,當(dāng)冗余容錯(cuò)電路面積小于最小缺陷團(tuán)面積時(shí),相應(yīng)成團(tuán)因子的值只取決于缺陷團(tuán)內(nèi)缺陷相關(guān)性的強(qiáng)弱,與冗余容錯(cuò)電路面積無(wú)關(guān);當(dāng)冗余容錯(cuò)電路面積大于最大缺陷團(tuán)面積時(shí),此時(shí)成團(tuán)因子不僅受缺陷成團(tuán)性強(qiáng)弱的影響,而且隨冗余容錯(cuò)電路面積的變化而變化。

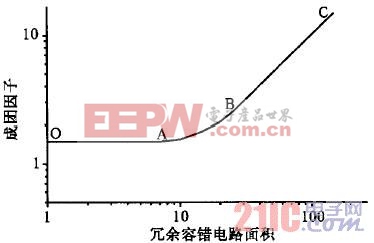

圖2 成團(tuán)因子α與冗余容錯(cuò)電路面積的關(guān)系

IC成品率預(yù)計(jì)常用到負(fù)二項(xiàng)式分布模型,此模型中的參數(shù)α是模型的成團(tuán)因子。Stapper采用回歸分析法分析驗(yàn)證成團(tuán)因子α,得出成團(tuán)因子與冗余容錯(cuò)電路面積的關(guān)系,如圖2所示。曲線中的OA水平直線段表示α維持不變,對(duì)應(yīng)冗余容錯(cuò)電路面積小于所有缺陷團(tuán)面積的情況;曲線中的BC直線段表明α與冗余容錯(cuò)電路塊面積成正比,對(duì)應(yīng)冗余容錯(cuò)電路面積大于所有缺陷團(tuán)面積的情況; 曲線中的AB曲線段表明α隨冗余容錯(cuò)電路面積增大而呈現(xiàn)非線性增長(zhǎng),此時(shí)冗余容錯(cuò)電路面積介于最小缺陷團(tuán)面積和最大缺陷團(tuán)面積之間。

在沒(méi)有缺陷團(tuán)面積數(shù)據(jù)時(shí),一般假定FPGA內(nèi)缺陷團(tuán)面積小至邏輯塊,大至整個(gè)芯片,并且在這范圍內(nèi)連續(xù)分布。此時(shí)圖2中的點(diǎn)A、B分別趨近點(diǎn)O、C,在曲線整個(gè)范圍內(nèi),成團(tuán)因子隨冗余容錯(cuò)電路塊面積增大而呈非線性增長(zhǎng)。

實(shí)驗(yàn)數(shù)據(jù)表明,在冗余容錯(cuò)電路面積小于所有缺陷團(tuán)面積時(shí),成團(tuán)成子u維持不變。成團(tuán)因子α和u物理意義相同,遵循相似的變化規(guī)律。

缺陷成團(tuán)時(shí)提高冗余容錯(cuò)電路可靠性的策略

冗余容錯(cuò)電路的主份和備份電路布局于FPGA芯片內(nèi)。當(dāng)FPGA內(nèi)缺陷成團(tuán)時(shí),可以通過(guò)調(diào)整布局,增大主、備份電路的幾何距離,降低冗余容錯(cuò)電路的失效率。

分析表明,在缺陷成團(tuán)時(shí),冗余容錯(cuò)電路的失效率取決于所對(duì)應(yīng)成團(tuán)因子的大小。成團(tuán)因子決定于冗余容錯(cuò)電路的等效面積。冗余容錯(cuò)電路的等效面積等于涵蓋整個(gè)冗余容錯(cuò)電路的最小面積,如圖3所示。增大主、備份電路的幾何距率,就是增大冗余容錯(cuò)電路的等效面積,從而增大對(duì)應(yīng)成團(tuán)因子的值。增大成團(tuán)因子,就能降低冗余容錯(cuò)電路的失效率,提高其可靠性。

圖3 冗余容錯(cuò)電路布局示意圖

DIY機(jī)械鍵盤(pán)相關(guān)社區(qū):機(jī)械鍵盤(pán)DIY

評(píng)論