QIC 在縮短大容量FPGA編譯時間中的作用

前言

按照相對論的理論,時間也是可以被拉長縮短的,只不過需要巨大的能量支撐著您達到一個和光速可比擬的高速度而已。這話說著輕松,你我心里都明白,估計咱們的有生之年是看不到這樣的情景的……

回到可編程邏輯器件領域,隨著65nm、40nm,乃至目前的28nm深亞微米工藝的采用,廠家生產出了越來越大,也越來越復雜的FPGA器件。而用戶們在為FPGA不斷增強的功能和不斷下降的單位成本而欣喜不已的同時,也在為相關EDA軟件的性能滯后所帶來的開發效率相對降低而苦惱不已,尤其是對大容量FPGA芯片動輒10到20個小時的編譯時間可謂怨氣沖天。筆者在許多次面對一線的FPGA工程師時,都聽到了這樣類似的話:要是編譯時間能壓一壓就好了!

Altera不能真的壓縮時間,但我們能改變“速度”!從數年前的版本開始,Quartus2軟件中就整合了一種新技術,或者說一種新的設計流程:增量式編譯(Incremental Compilation)。它是ALTERA為解決大容量FPGA設計編譯時間太長的問題給出的一個新式工具!您,了解它嗎?

增量式編譯原理及流程

增量式編譯QIC的原理很容易理解:對一個復雜的設計而言,肯定是需要做一定的功能劃分,由不同的子功能模塊來實現。那么在設計進入后期比較成熟的時候,前后兩次編譯的設計版本中,會有很大部分的電路邏輯都是相同的(沒有修改),如果能在后一次編譯中,重復利用前一次編譯中未改變部分的編譯結果,也就是相應部分的布局布線信息,那么就能把這部分邏輯所消耗的布局布線時間節約下來,從而在很大程度上縮短整個設計的編譯時間。當然,聰明的讀者都能想到,這樣的編譯方式,除了能縮短編譯時間,還能支持許多別的用途,比如IP設計交付、團隊開發、不改變正常設計結果插入調試接口等。這些確實都是ALTERA 增量式編譯能夠實現的功能,但在本文中我們只闡述QIC在縮短編譯時間方面的作用。

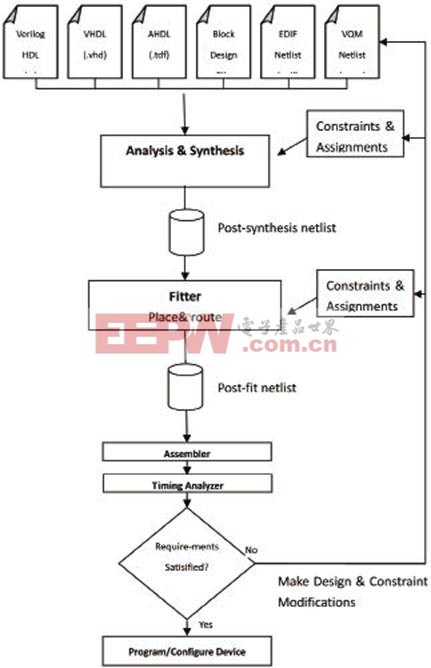

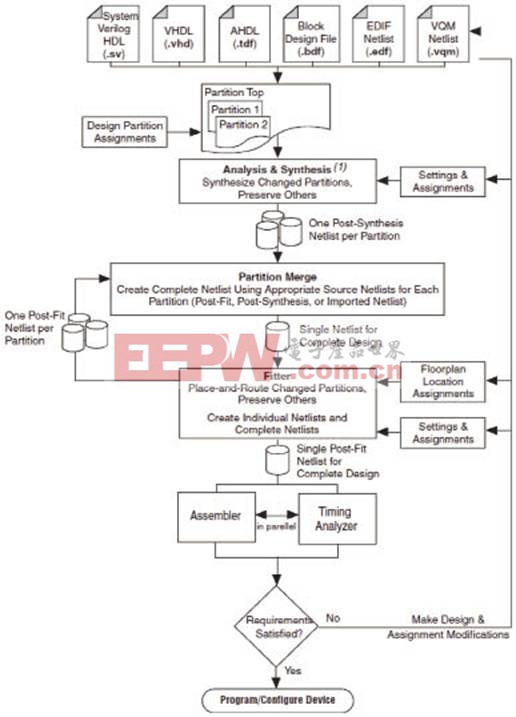

增量式編譯原理雖然簡單,但要在FPGA的EDA軟件中實現,卻是一個復雜的系統工程。它不是簡單地在軟件中增加一個功能模塊,而是對編譯處理流程多方面的改變和增強!請比較圖1和圖2兩幅附圖:圖1是傳統的FPGA編譯流程(Altera名稱:Flat compilation),圖2則是增量式編譯流程的示意圖。我們很容易發現增量式編譯流程復雜了許多,不僅引入了一些新的概念,比如設計分區(partition)、分區綜合后網表、分區布局/布線后網表等,同時加入了新的處理階段——分區合并(partition merging),而且對分析綜合(AnalysisSynthesis)和布局布線(fitter)階段進行了改進,增加了許多針對分區的具體操作。

圖1 Flat Compilation 流程

圖2 QIC增量式編譯流程

經過幾年的研究與實踐,QuartusII的增量式編譯已逐步完善,無論是在可操作性、穩健性方面,還是在縮短編譯時間的效果方面,都十分出色。筆者參與的幾個客戶項目中,通過QIC的實施,都得到了50%左右的編譯時間節約,極大提高了客戶的開發效率。下面,我將結合這些實際項目中的經驗,介紹如何實踐利用QIC來高效的縮短設計編譯時間。

QIC實踐

QIC的效果評估

在討論具體如何使用QIC之前,先考慮一個問題:如果讀者在您的工作中使用了增量式編譯QIC,怎么評估它的效能呢?

您需要至少做3輪實驗,才能看到QIC節約編譯時間的效果。首先,需要把您的設計用傳統編譯流程Flat Compilation進行編譯,記錄下各階段所花費的時間。然后,創建合理的設計分區,指定分區網表性質,進行第二次編譯,得到QIC各個分區的初始網表,并請記錄下操作時間。第三次編譯,您可以選擇修改設計中的某一個分區,然后再編譯一次,記錄下操作花費的時間。將第三次的編譯時間和第一次相比,正常的話應當看到非常明顯的時間節約,這才是QIC增量式編譯在編譯時間節約方面的體現。

值得注意的是,第二次編譯中已經使用了QIC,但往往花費時間和第一次編譯差不多,有時還有增長。許多人為此懷疑QIC的性能,認為QIC沒有效果甚至惡化了編譯時間。這其實是一種誤解!為什么呢?回到圖2,我們可以看到,QIC流程在AnalysisSynthesis和fitter之間增加了一個新的處理階段——分區合并,它是需要額外花費在第一次Flat Compilation中不存在的時間。而且,由于這是創建分區后的第一次編譯,所有分區的網表都是空白的,也就是說整個設計都需要被編譯、分析、綜合、布局布線等的工作量和第一次編譯是類似的,因此這部分花費的時間也是差不多。把這兩部分時間加起來,自然第2次編譯時間有可能會比第一次長了。只有當進行第3次編譯的時候,各個分區都有可重用的網表了,才有可能將那些沒有設計改變的分區的網表重用,從而節約綜合和布局布線階段的時間,達到整體編譯時間的節約。

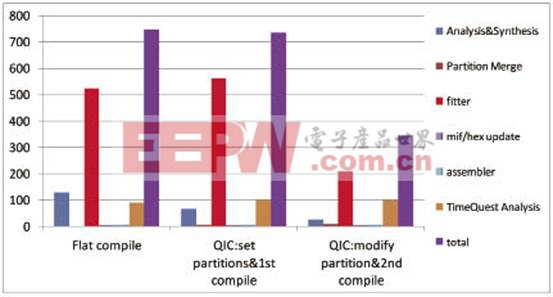

圖3是筆者支持的一個客戶所進行的QIC增量式編譯性能評估的結果總結。客戶的設計是高端路由器中的包處理應用,使用了ALTERA公司的Stratix4GX530器件,邏輯利用率大約是60%。客戶的編譯硬件是一臺高性能服務器:、

圖3 Z客戶增量式編譯評估實驗效果

• CPU:16core Intel(R) Xeon(R) CPU E7420 @2.13GHz

• Memory:64GB

即使是如此,在不使用QIC的情況下,客戶的每次編譯都需要12到13個小時。而在使用QIC并根據QIC指導原則進行了必要的設計優化后,最好的實驗結果是可以在6個小時左右(大約350分鐘)完成一次編譯,節約了接近55%的總編譯時間!從圖3中很容易看出前面文字描述的幾個特點:

1. 第一次編譯和第二次編譯的總時間差不多(750 VS 730)

2. 第三次編譯中,AnalysisSynthesis操作的時間,fitter操作得時間都比第一次編譯有非常明顯的降低;

3. 從原理上看,QIC的網表重用對Assembly和時序分析沒有直接影響。因此三次編譯中,Assembler和時序分析所花費的時間是差不多的。

QIC指導原則

合理創建分區

Quartus中的“分區”是和設計層次緊密關聯的。任何設計,無論簡單還是復雜,都會有一個頂層模塊(top-level module),Quartus自動將它設置為一個默認分區(命名為top),不需要用戶設定。而別的分區,需要用戶手動創建。創建分區的方法很簡單,在Quartus GUI界面左上角的Hierarchy窗口,選擇想創建分區的實體,右鍵喚出的菜單中選擇“Design Partition”,然后在下一級菜單中選擇”Setting as Design Partition”,分區就創建成功了。

從圖2可以看出,分區(Partition)是增量式編譯中的一個關鍵概念。Altera規定:只要是有完整設計邊界的設計實體,無論它在設計的哪一層次,都可以用它來創建設計分區。也就是說,Quartus II中,設計中任何層次中的任何一個設計模塊,可以作為一個設計分區;一個設計中也可以包含不止一個設計分區;即使是在設計的同一層次,也可有多個分區。同時,請注意:分區之間沒有層次關系,任何邏輯只能歸屬于某一個分區。以圖5為例,A模塊由A1、B1、C1三個子模塊組成。如果A模塊被設置為分區,Quartus會用模塊名來為此分區命名:A分區。那么,A分區中就會包含A1、B1、C1三個子模塊的所有邏輯。但如果把B1子模塊也創建為分區,那么,A分區中就只包含A1、C1兩個子模塊的邏輯,B1子模塊的邏輯只屬于新的B1分區了。

評論