基于消息機制的片上多處理器系統的研究

摘要:描述了一種基于消息機制構建的片上多處理器系統。該系統采用主從結構,運用消息進行通信,并且從處理器之間彼此相互獨立,在硬件結構與軟件設計上保持一致。這樣不僅簡化了系統的設計,更使得系統具有一定的容錯性與穩定性。最后在Quartus軟件中設計并且綜合,在該系統下運行JPEG編碼算法,當運行于100 MHz時,測得系統在不同個數處理器時的處理性能,滿足了設計要求。

關鍵詞:多處理器;消息機制;FPGA;DMA

引言

如今,數字處理技術已得到了廣泛的應用,各種復雜算法的提出與處理精度的提高,都使得需要處理的數據量變得越來越大。而提高系統處理性能主要有提高處理器的頻率、采用多處理器系統2種方法。在單處理器頻率提升達到瓶頸的情況下,多處理器系統成為提高系統性能的一種有效方式。

近年來,多處理器系統的應用已經越來越廣泛,但大部分的多處理器系統都是針對特定的應用對象進行設計,這類系統耦合度高,任務分解充分,執行效率高。同時,這類系統開發難度較大,針對性強,不具有通用性,且當系統中的某個處理器出現問題時,整個系統將面臨崩潰。為了簡化系統設計,提升多處理器系統的穩定性,本文提出了一種基于消息機制構建的多處理器系統。該系統采用主從結構,主處理器運行管理系統,從處理器完成用戶指定的任務。從處理器彼此之間相互獨立,可相互替代,并在硬件結構與軟件設計上保持一致。這樣不僅簡化了系統的設計,更使得系統具有一定的容錯性與穩定性。實驗結果表明,本設計達到了預期效果。

1 多處理器系統體系結構

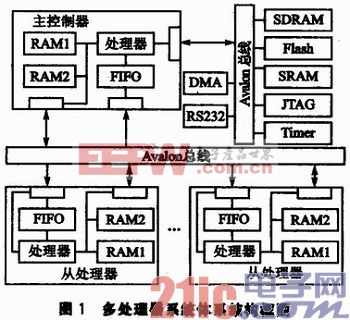

本文所設計的多處理器系統體系結構框圖如圖1所示,它主要包括一個主控制器模塊及多個從處理器模塊。

主控制器主要負責消息的分配與跟蹤,控制DMA進行數據的快速移動等。從處理器則根據主控制器分配的任務執行相應的處理。系統上還集成了多種系統外設,如RS232、定時器、JTAG接口、多種存儲控制器等。

主控制器模塊及從處理器模塊中使用的處理器是Nios Ⅱ嵌入式軟核處理器,選用的是快速型。該處理器是Altera公司推出的32位RSIC嵌入式處理器,可根據需要配置為快速、標準、經濟3種類型,提供滿足性能與成本的最佳方案。每個模塊中都配備1個FIFO,用于存儲消息;配備2個RAM存儲器,組成乒乓結構,用于存儲原始數據或結果數據,同時可用于DMA傳輸控制。

主控制器模塊與多個從處理器模塊構成主從結構。主控制器集中管理所有的從處理器模塊;所有的從處理器模塊相互獨立,互不影響,運行時可相互替代。主控制器模塊與系統的所有外設及所有的從處理器模塊都是通過Avalon總線相互連接。該總線是一種協議較為簡單的片內總線,處理器可通過該總線與外界進行數據交換。

2 通信機制的設計

在本文所設計的系統中,各個模塊之間都采用消息進行通信,如主控制器與從處理器之間的通信、處理任務的分配、處理結果的反饋等。對于數據的傳遞,如果數據量比較小,可以把數據附在消息中進行傳遞;如果數據量比較大,則用DMA進行存儲器到存儲器之間的快速移動。

2. 1 消息結構的設計

消息是該系統的通信基礎,也是系統運行的重要環節,因此定義一種結構通用又易于識別的消息結構顯得十分重要。在該系統中,采用的是可變長度的消息結構:{類型;長度;子類型;參數1;參數2;…;參數N}。

其中長度指的是其后的數據個數,不包括類型及自身。這樣處理有利于消息的傳遞與讀取。在消息結構中,類型、長度、子類型這3個字段在消息中的位置固定,有利于消息的解析。如根據消息中的類型與子類型字段,可快速轉到相應的處理函數進行處理,根據長度字段,可準確地判斷消息中參數的個數;將“子類型”排在“長度”之后,則有利于消息的讀取。

2.2 消息的傳遞

消息的傳遞過程就是向目標消息存儲器FIFO寫入消息數據的過程。由于系統采用的是主從結構,當消息在控制器與處理器之間的不同方向傳遞時,傳遞過程并不相同。

評論