基于FPGA的微電網并網控制器的設計與實現

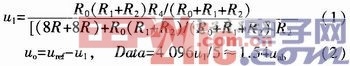

采樣電路輸入輸出關系為:

式中:Data為A/D轉換數值。

3.2 鎖相模塊設計

3.2.1 改進算法鎖相原理分析

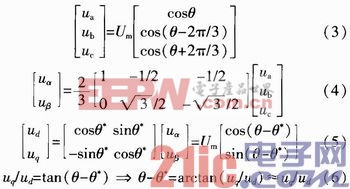

基于同步旋轉坐標的鎖相算法實現過程如下,ua,ub,uc為三相對稱電壓,Um為相電壓峰值,uα,uβ,ud,uq分別為兩相靜止、同步旋轉坐標系下電壓,θ,θ*分別為電網電壓、鎖相環輸出的相角。

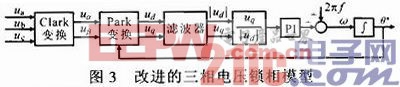

綜上可知,通過ud/uq即可消除Um帶來的影響。改進后的同步坐標變換下三相電壓鎖相模型如圖3所示。本文引用地址:http://www.104case.com/article/189724.htm

3.2.2 鎖相環濾波器的設計

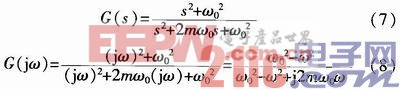

濾波器的設計目標是使系統在擾動信號頻率附近快速地衰減,而不對其他頻率造成衰減,從而使系統具有較高的抗干擾性和良好的動態性能。這里選用陷波器,陷波器可理解為低通濾波器和高通濾波器的級聯,其典型傳遞函數如下:

令ω0=628 rad·s-1,使系統具有良好的動態性能,假設系統頻率特性曲線在兩倍工頻附近(ω=622~634 rad·s-1)的斜率k≤-40dB/ dec,使系統在擾動信號附近快速衰減,即|G(jω)|≤0.01。可得m≥0.96,取m=0.96,綜上可得濾波器傳遞函數為:

![]()

3.2.3 鎖相環PI參數的設計

系統的開環傳遞函數為:

![]()

假定系統的總調節時間大于10倍陷波器的調節時間,則陷波器的傳遞函數可近似為1,系統開環傳遞函數進一步簡化為:

![]()

對照典型二階系統可得:![]() 。令ξ=0.8,陷波器時間常數ts1≈10/(mω0),根據假定PI調節器時間常數為陷波器的10倍,即ts=5/(ξωn)=10ts1,kp=mω0/10≈60.3,τ=40ξ2/(mω0)≈0.04。

。令ξ=0.8,陷波器時間常數ts1≈10/(mω0),根據假定PI調節器時間常數為陷波器的10倍,即ts=5/(ξωn)=10ts1,kp=mω0/10≈60.3,τ=40ξ2/(mω0)≈0.04。

評論