基于FPGA的微電網并網控制器的設計與實現

摘要:針對微電網與大電網能量交互的問題,設計了一種基于現場可編程門陣列(FPGA)實現的微電網并網控制器。該并網控制器以ADS7864芯片為核心實現數據的的同步采樣;同時,根據鎖相原理,研究了一種改進的基于同步空間坐標變換的鎖相控制算法,給出了鎖相環模塊中濾波器和PI調節器參數的設汁方法。通過Matlab/Simulink仿真分析驗證了鎖相環的有效性,最后研制出基于FPGA實現的并網控制器并應用于微電網實驗平臺。實驗表明該控制器能實現快速準確的數據采集和鎖相控制,從而實現微電網的平滑并網。

關鍵詞:微電網;控制器;并網;現場可編程門陣列

1 引言

微電網是智能電網的一個重要發展方向,能很好解決單個分布式發電單元獨立接入給大電網造成的不穩定,從而為大電網提供有力的支撐。

微電網中的并網控制器主要由同步數據采樣模塊、數字鎖相模塊和并網算法模塊構成。基于文獻,在此設計了一種改進的基于同步坐標變換的動態鎖相環,該鎖相環能消除電網電壓幅值波動帶來的影響,從而有效克服零點檢測法、靜止坐標系法和普通同步坐標變換方法的不足。

首先介紹了并網控制器的總體設計,然后對并網控制器的數據采樣模塊、鎖相控制模塊和并網算法模塊進行詳細分析。最后研制出基于FPCA實現的并網控制器,實驗證明所設計的并網控制器能較好地實現微電網的并網控制。

2 系統總體設計

所設計的并網控制器由同步數據采樣模塊、數字鎖相模塊和并網算法模塊構成。12位六通道低功耗高速同步采樣芯片ADS7864負責數據的同步采集,FPGA負責整個系統的驅動控制,主要包括數據采樣模塊的驅動、數字鎖相算法的實現及并網控制算法的實現。系統工作原理:同步采樣模塊實時采集電網側和微電網側母線電壓;FPGA根據采樣信號結合所提出的鎖相算法對電網側和微電網側的電壓進行鎖相控制;并網算法模塊根據并網條件進行判斷,當滿足并網條件時發出并網命令完成微電網并網。

3 關鍵技術研究

3.1 同步采樣模塊設計

數據采集原理:采用ADS7864芯片實現電網側和微電網側電壓采集,芯片基準電壓為2.5 V,輸入電壓范圍為0~5 V。A/D轉換結果y與輸入模擬信號量x之間的關系式為:y/4 096=(2.5-x)/5。

采樣電路的設計:分壓電路拓撲結構如圖1所示,圖中,利用串聯電阻分壓,然后通過求差電路將差分線電壓轉換成單端電壓值,并引入箝位二極管防止電壓過大損壞芯片。其中R=390 kΩ,R0=110 kΩ,R1=R2=30 kΩ,R3=R4=9.1 kΩ。

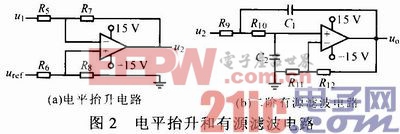

ADS7864芯片的輸入電平范圍為0~5 V,而采樣信號為正弦交流信號,采用減法器電路實現電平的抬升。抬升電平參考電壓uref由ADS7864芯片提供,電平抬升電路如圖2a所示,其中R5=R6=R7=R8=22 kΩ。

采用二階有源低通濾波電路對采樣信號進行濾波處理,濾波電路結構如圖2b所示。其中R9=R10=R11=10 kΩ,R12=0,C1=C2=5.6 nF,該濾波器對信號的放大倍數A=1+R12/R11=1,截止頻率fc=1/![]() 。

。

評論