基于DSP+FPGA汽車防撞報(bào)警設(shè)備高速數(shù)據(jù)采集

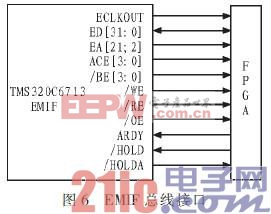

本系統(tǒng)在設(shè)計(jì)中DSP主要是通過(guò)C6713器件的外部存儲(chǔ)器接口EMIF與FPGA進(jìn)行數(shù)據(jù)通信。外部存儲(chǔ)器接口(EMIF)是TMS DSP器件上的一種接口。一般來(lái)說(shuō),EMIF可實(shí)現(xiàn)DSP與不同類型存儲(chǔ)器(SRAM、Flash RAM、DDR-RAM等)的連接。用EMIF與FPGA相連,從而使FPGA平臺(tái)充當(dāng)一個(gè)協(xié)同處理器、高速數(shù)據(jù)處理器或高速數(shù)據(jù)傳輸接口。

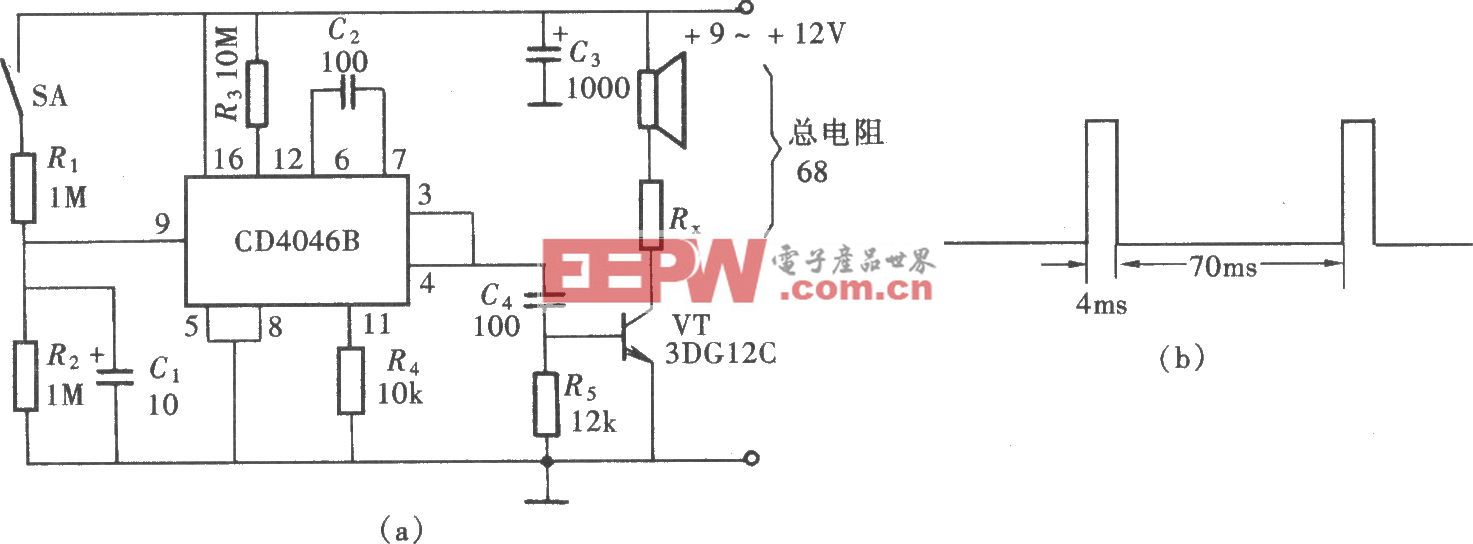

其EMIF的總線接口圖如圖6所示。

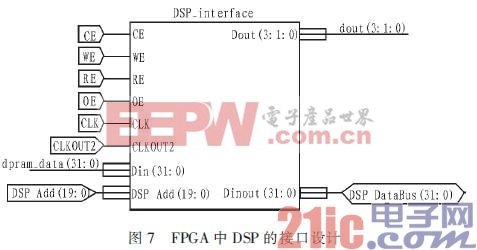

在完成對(duì)EMIF的DSP配置后,接下來(lái)就是實(shí)現(xiàn)EMIF接口的FPGA配置工作,保證FPGA中的數(shù)據(jù)正常的讀入到DSP中。在FPGA中配置EMIF接口的連接圖如圖7所示。

該模塊是DSP與FPGA進(jìn)行通信的接口模塊。通過(guò)該模塊,DSP可以實(shí)現(xiàn)向FPGA傳輸控制信號(hào),F(xiàn)PGA也可以通過(guò)該模塊將FIFO中的數(shù)據(jù)傳給DSP。CE、WE、RE、OE為DSP輸入的使能信號(hào),CLK為FPGA提供內(nèi)部時(shí)鐘,CLKOUT2是EMIF的輸出時(shí)鐘,為DSP與FPGA通信提供時(shí)鐘頻率,DSP_Addr(19:0)為DSP的輸入地址,DSP_DataBus(31:0)為DSP的數(shù)據(jù)總線。FPGA根據(jù)讀使能信號(hào)OE與片選信號(hào)CE的輸入邏輯來(lái)判斷EMIF是進(jìn)行讀操作還是寫操作。當(dāng)DSP通過(guò)EMIF讀取數(shù)據(jù)時(shí),F(xiàn)PGA中的數(shù)據(jù)從dpram_data(31:0)輸入,由DSP_DataBus(31:0)管腳傳送給DSP;若寫數(shù)據(jù),將DSP_DataBus(31:0)傳來(lái)的數(shù)據(jù)從dout(31:0)送入FPGA。

2.4 人機(jī)交互模塊

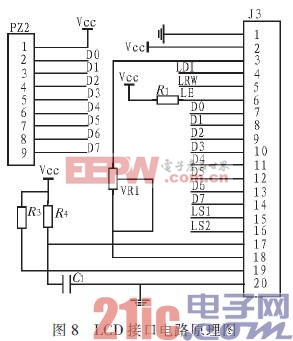

人機(jī)交互模塊分為按健電路和LCD顯示電路。限于篇幅,本文僅介紹LCD電路。

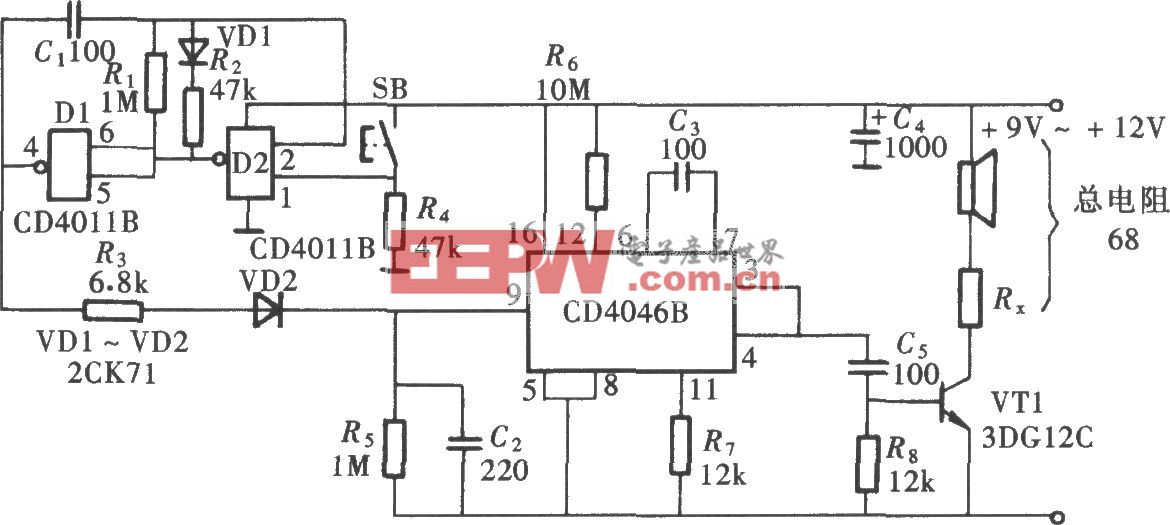

LCD顯示部分我們采用真空熒光顯示點(diǎn)陣式VFD屏,其優(yōu)點(diǎn)是能高亮度發(fā)光。由于我們選擇的屏是5 V供電,所以由DSP過(guò)來(lái)的3.3 V的信號(hào)線需要經(jīng)過(guò)74LVCA245轉(zhuǎn)化為5 V,再與VFD屏的控制器接口相連,LCD控制器接口如圖8所示。

fpga相關(guān)文章:fpga是什么

評(píng)論