基于CPLD的軟開關電源數字控制器設計

1 引言

本文引用地址:http://www.104case.com/article/189673.htm近年來,隨著大功率開關電源的發展,對控制器的要求越來越高,開關電源的數字化和智能化也將成為未來的發展方向。

目前,我國的大功率開關電源多采用傳統的 模擬控制方式,電路復雜,可靠性差。因此,采用集成度高、集成功能強大的數字控制器設計開關電源控制器,來適應不斷提高的開關電源輸出可編程控制、數據通訊、智能化控制等要求。

2.數字控制器設計

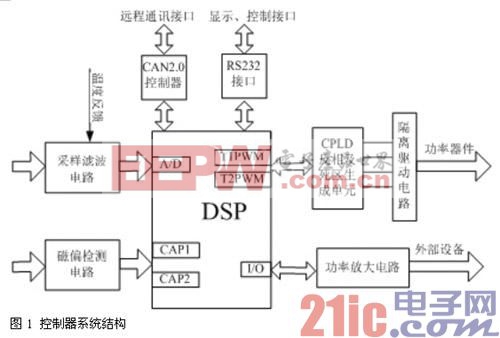

本文設計的數字控制器,采用TI公司24X系列DSP控制器中的TMS320LF2407A芯片作為主控制器,主要功能模塊包括:(1)DSP與可編程邏輯器件CPLD相配合實現全橋移相諧振軟開關驅動(2)偏磁檢測電路;(3)其他功能,如數據采集、保護及外部接口等。控制系統結構如圖1所示。

2.1移相控制波形的生成

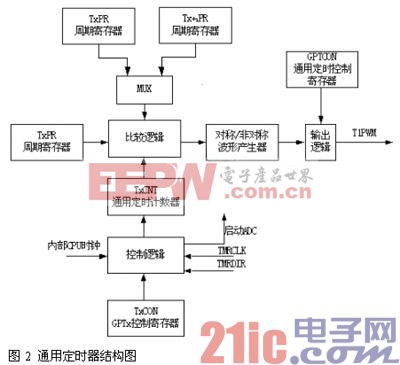

TMS320LF2407A芯片包含兩個事件管理器EVA和EVB,每個事件管理器都包括兩個通用定時器,通用定時器GPT1和GPT2對應于事件管理器EVA,GPT1和GPT2對應于事件管理器EVB,通用定時器的結構如圖2所示。

通用定時器是PWM波形產生的基礎,每個通用定時器都可以提供一路單獨的PWM輸出通道。獲得指定周期指定脈寬的PWM信號的過程是:首先設置通用定時器 控制寄存器TxCON確定計數器的計數模式和時鐘源;然后根據需要的PWM波形周期設置周期寄存器TxPR;接著裝載比較寄存器TxCMPR,確定PWM 波形的占空比。通過上述相應的設置即可獲得指定周期、指定脈寬的PWM信號。

而輸出移相波形的關鍵是讓同一事件管理器中的兩個通用定時器同步工作,并且在一個通用定時器從零開始計數的時刻,賦予另一個通用定時器計數器不同的初值, 初值的大小決定兩個通用定時器輸出PWM波形的相位關系。本文利用事件管理器EVA的兩個通用定時器GPT1和GPT2的同步工作,產生移相波形。

為了避免因開關器件特別是IGBT器件在關斷時電流拖尾造成橋臂瞬時直通所造成的危害,還需要在同側橋臂的開關器件控制波形中添加死區。因為PLD具有可 在線修改能力,可在PCB電路完成后隨時修改設計,而不必改動硬件電路,因此本文采用ALTERA公司的EPM7000S系列的CPLD芯片,通過編程生 成控制波形的死區。如圖3所示。

評論