基于FPGA的面陣CCD成像系統設計

視頻信號處理單元主要完成預放、濾波、相關雙采樣(CDS)、后置放大以及A/D轉換等功能。本文采用集成圖像處理芯片VSP2230。VSP22 30是一款集成圖像處理芯片,它可以對CCD輸出信號進行相關雙采樣,具有可編程暗電平校正、可編程增益放大器(放大范圍為-6~42 dB)、將模擬信號轉換為十位的數字信號等功能。

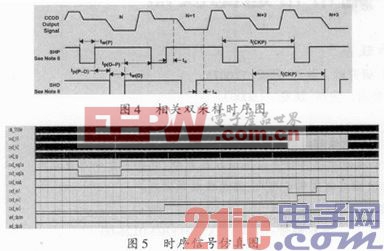

相關雙采樣(CDS)單元是對每個像元信號采樣兩次,分別獲得參考電平和信號電平,將兩個電平值的差作為CCD的輸出信號,通過相關雙采樣可以濾除復位噪聲、輸出放大器的白噪聲以及1/f噪聲等。

具體模式見圖4,在嵌位脈沖SHP的上升沿采集參考電平信號,在采用脈沖SHD的上升沿采集信號電平。SHP和SHD的位置很重要,對信號質量影響。很大,需要精細調整。ICX415AL芯片的每一行前端有3個啞像元,后端有38個暗像元,通過測量這些像元的電荷量,可以獲得該款CCD的暗電平值,將上文的輸出信號再減去暗電平值,就可去除暗電流噪聲,輸出更準確的信號。VSP2230芯片有兩個引腳即用來完成該任務,即CLPDM和CPLOB引腳。

在CCD輸出暗像元時,將CPLOB置為低電平,其他時候恒為高電平,在CCD輸出啞像元時,將CLPDM置為低電平,其他時候置為高電平。本文引用地址:http://www.104case.com/article/189623.htm

最后將模擬信號經A/D轉換為10位數字信號,輸出給FPGA,再經圖像采集卡輸出至顯示設備,即可觀看到視頻圖像。

3 波形仿真結果

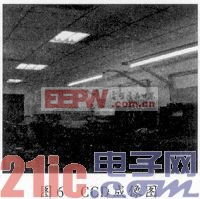

本設計采用Altera公司的Cyclone系列的EP1C12F25617芯片,在QuartusⅡ9.1集成開發環境下,運用VHDL語言進行編程,利用Modelsim SE 6.5仿真工具進行仿真,如圖5所示,時序滿足芯片手冊要求。

4 實驗結果

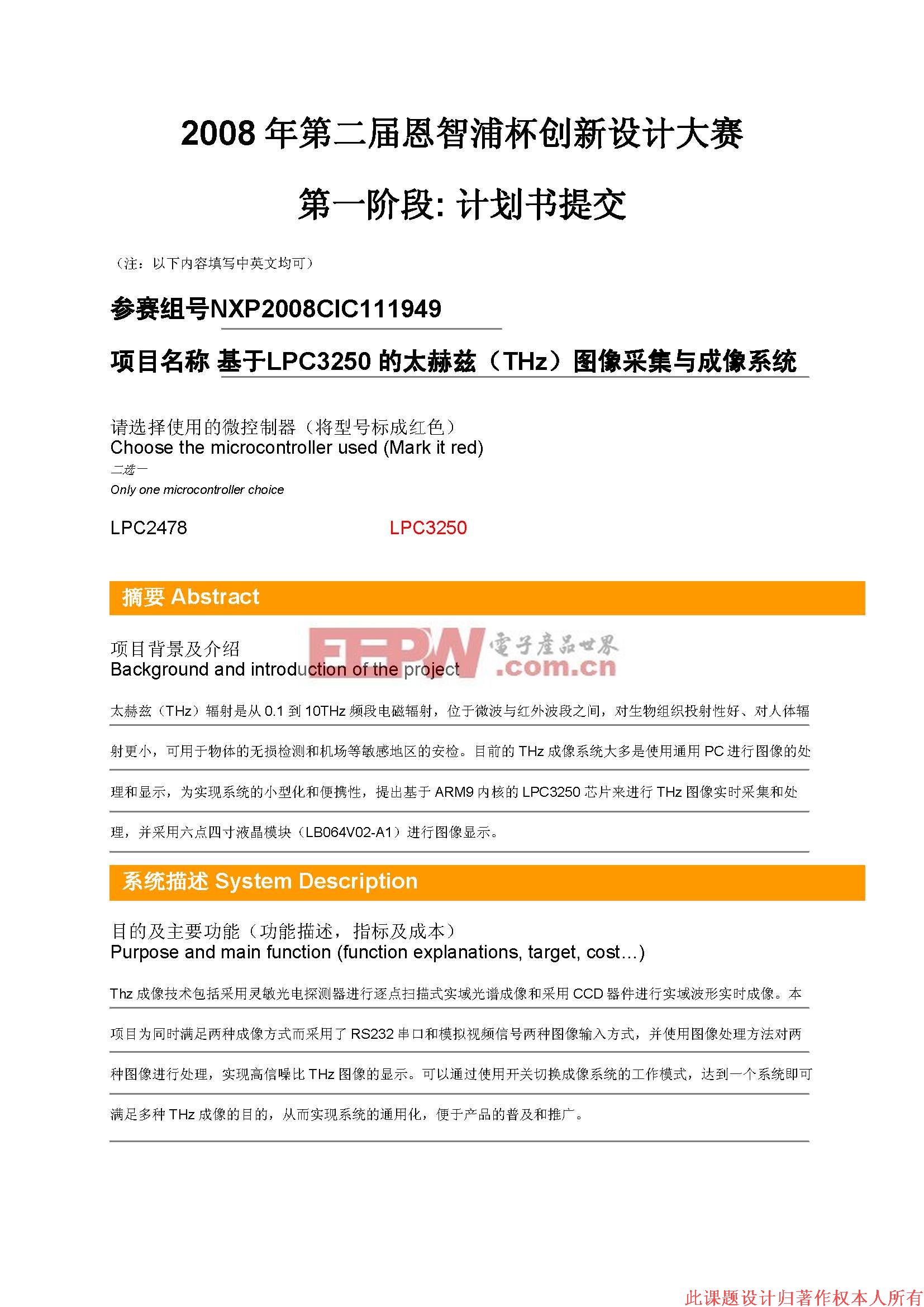

將用VHDL語言編寫好的程序下載到FPGA中,用示波器檢測波形無誤后,接上CCD芯片,將圖像信號經LVDS采集卡采集后顯示于電腦上,如圖6所示,由圖可知,該CCD成像系統成像效果良好,符合設計要求。

5 結論

在分析了SONY ICX415AL行間轉移型面陣CCD的驅動時序的基礎之上,提出了基于FPGA的驅動時序發生器的設計方案,并使用VHDL語言實現了該設計方案。整個設計充分結合了FPGA器件的設計簡單、調試靈活、性能優越等優點和VHDL語言的硬件描述能力強、便于學習和理解等優點。該CCD相機具有每秒50幀的幀頻,適用于觀測高速運動的物體,成像效果良好,目前已運用于實際工程中。

fpga相關文章:fpga是什么

電荷放大器相關文章:電荷放大器原理 熱成像儀相關文章:熱成像儀原理

評論