基于FPGA的面陣CCD成像系統(tǒng)設(shè)計

摘要:采用SONY行間轉(zhuǎn)移型面陣CCD ICX415AL作為圖像傳感器,設(shè)計了一款新型CCD成像系統(tǒng)。以Altera公司的FPGA芯片EP1C12F256作為時序發(fā)生器產(chǎn)生CCD驅(qū)動信號。采用相關(guān)雙采樣技術(shù)濾除了視頻信號中的相關(guān)噪聲,提高信噪比。在QuartusⅡ9.1開發(fā)環(huán)境下采用VHDL編程,并利用Modelsim SE 6.5仿真軟件進行訪真測試。實驗結(jié)果表明,所設(shè)計的時序滿足ICX415AL的時序要求,在29.5 MHz的時鐘驅(qū)動下,每秒輸出50幀圖片,能滿足高速跟蹤要求。

關(guān)鍵詞:行間轉(zhuǎn)移型面陣CCD;驅(qū)動時序;相關(guān)雙采樣;FPGA

0 引言

CCD(Charge Coupled Device)是20世紀(jì)70年代初發(fā)展起來的新型半導(dǎo)體集成光電器件,它可以把通過光學(xué)鏡頭投影到其上的景物可見光信號轉(zhuǎn)換成比例的電荷包,并在適當(dāng)?shù)臅r鐘脈沖的驅(qū)動下進行定向轉(zhuǎn)移,從而輸出成為電壓視頻圖像。CCD具有集成度高、功耗小、體積小、工作電壓低、靈敏度高等優(yōu)點,目前已廣泛應(yīng)用與空間遙感、對地觀測等領(lǐng)域。

按結(jié)構(gòu)分類,CCD可分為線陣CCD和面陣CCD,而面陣CCD按排列方式又可分為全幀轉(zhuǎn)移(Full Frame)CCD、幀轉(zhuǎn)移(Frame Transfer)CCD以及行間轉(zhuǎn)移(Interline Transfer)CCD。三種類型的CCD各有優(yōu)缺點,其中行間轉(zhuǎn)移CCD不需要機械快門,速度最快,最適合用于觀測快速運動的物體。本文設(shè)計了一種行間轉(zhuǎn)移型面陣CCD的高速驅(qū)動電路。

1 行間轉(zhuǎn)移型面陣CCD的結(jié)構(gòu)和工作模式

本設(shè)計采用的是SONY公司的ICX415AL型號CCD芯片,ICX415AL是行間轉(zhuǎn)移型面陣CCD,對角線為8 mm,尺寸為8.3 μmx8.3 μm,總像元素為823(H)×592(V),有效像元為782(H)x582(V)。它不僅具有高靈敏度、低暗電流的特性,而且還具有優(yōu)秀的抗開花技術(shù)。ICX415AL還具有連續(xù)可變的電子快門功能,可以通過控制曝光時間,獲得不用曝光條件下的圖像。

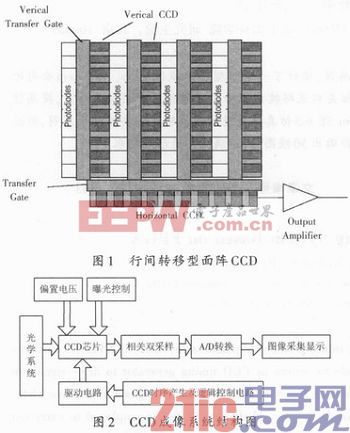

ICX415AL的結(jié)構(gòu)如圖1所示。其中,感光單元與存儲單元相鄰排列,相當(dāng)若干個單邊傳輸?shù)木€陣CCD按垂直方向排列,在積分時間結(jié)束后,感光單元電荷轉(zhuǎn)移到相鄰的存儲單元,在垂直轉(zhuǎn)移脈沖V1,V2,V3的共同作用下一行一行的轉(zhuǎn)移至水平移位寄存器,在水平轉(zhuǎn)移脈沖H1,H2和復(fù)位脈沖RG的共同作用下經(jīng)放大器讀出。

2 行間轉(zhuǎn)移面陣CCD的驅(qū)動電路設(shè)計

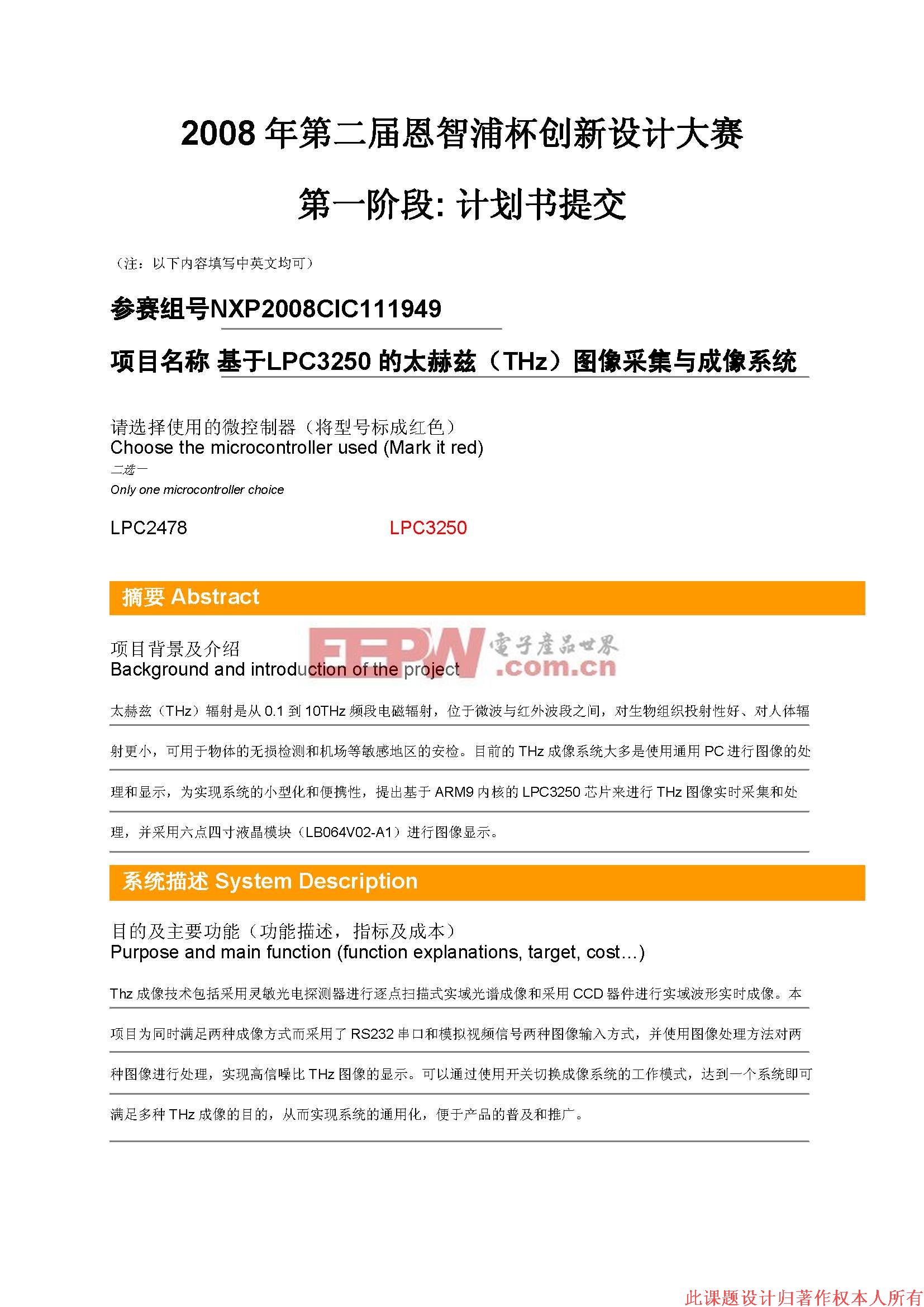

整個電路設(shè)計如圖2所示,它主要包括偏置電路、時序驅(qū)動電路、視頻信號處理單元等。下面分別介紹這幾個部分。

ICX415AL偏置電路設(shè)計包括電源電壓以及各種驅(qū)動時序電壓。經(jīng)仔細(xì)分析得出,CCD的垂直轉(zhuǎn)移信號電壓為-7.5 V,0 V,15 V三個級次,水平移位信號和復(fù)位信號電壓為5 V,基底信號電壓為22.5 V,FPGA供電電壓為3.3 V。綜合CCD供電系統(tǒng)要求,選用24 V作為外部電壓,使用YD12-24S15芯片獲得15 V和-12 V電壓,利用YDl6-24S05芯片獲得5 V電壓。分別將-12 V和5 V電壓經(jīng)過芯片LM2991和芯片LT1764EQ轉(zhuǎn)換為-7.5 V和3.3 V電壓,這樣就獲得了整個電路所需要的電壓。

時序驅(qū)動電路的設(shè)計比較復(fù)雜,對成像效果至關(guān)重要,因此,時序驅(qū)動電路的設(shè)計是整個系統(tǒng)的關(guān)鍵。ICX415AL芯片有3種驅(qū)動模式:逐行掃描模式、場讀出模式和中心掃描模式。其中逐行掃描模式具有較高的分辨率,且在29.5 MHz的時鐘驅(qū)動下可以達到每秒50幀圖像,滿足設(shè)計的需要,因此本設(shè)計采用逐行掃描模式。在該模式下,CCD需要7個驅(qū)動信號,垂直轉(zhuǎn)移時鐘V1,V2,V3,水平轉(zhuǎn)移時鐘H1和H2,復(fù)位時鐘信號RG,以及控制曝光時間的基底時鐘SUB。CCD的一個周期包括感光階段和轉(zhuǎn)移階段。在感光階段,給基底提供一個時鐘信號,在信號高電平期間,CCD處于偏置階段,開始收集電荷,儲存電荷的多少取決于外界光亮度以及曝光時間。當(dāng)垂直轉(zhuǎn)移時鐘V1,V2,V3出現(xiàn)一個如圖3所示的三相電平信號時,感光階段結(jié)束,成像單元電荷以電荷包的形式轉(zhuǎn)移到相鄰的存儲單元。轉(zhuǎn)移階段分為垂直轉(zhuǎn)移和水平轉(zhuǎn)移。垂直轉(zhuǎn)移包含625個循環(huán),每循環(huán)一次,電荷沿垂直方向移動一行,最后一行移入水平寄存器,然后在水平移位時鐘H1,H2和復(fù)位時鐘RG的作用下完成944個循環(huán),每次循環(huán)輸出一個像元信息。復(fù)位時鐘RG用于將浮置擴散節(jié)點的電荷清除掉,以便能準(zhǔn)確測量下一個點荷包。

fpga相關(guān)文章:fpga是什么

電荷放大器相關(guān)文章:電荷放大器原理 熱成像儀相關(guān)文章:熱成像儀原理

評論