基于FPGA的IRIG-B標準DC code編碼器VHDL設計

建立一個編碼器和計數器,在每個clkin時鐘到來時進行計數,判斷time_in的每位碼值和clrin計數值確定輸出脈寬,用上述同步分頻模塊(fenpin_e_clr)VHDL描述的方法實現輸出直流碼的時間起點與clr信號同步。

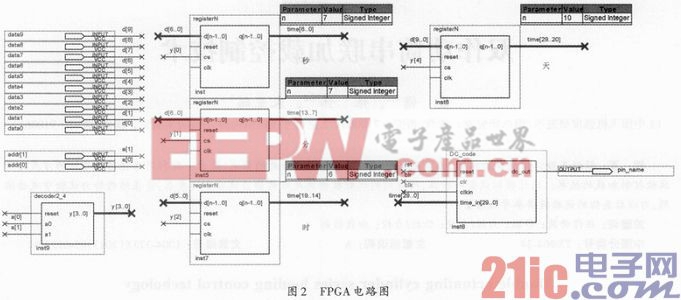

3 FPGA原理電路

IRIG-B碼編碼模塊通過端口從外部同步接收時間碼信息和準秒時刻,時間信息刷新頻率為1次/s。通過一個2位地址端口,一個10位數據端口,通過地址片選依次將‘秒’、‘分’、‘時’、‘天’信息送入不同的寄存器并經寄存器送IRIG-B DC碼編碼器的數據輸入端,由B碼

編碼器根據時鐘生成DC碼發送。其在FPGA內部實現電路原理如圖2所示。本文引用地址:http://www.104case.com/article/189622.htm

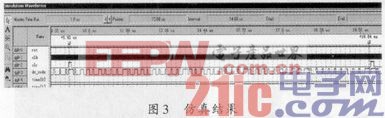

4 仿真

用QuartusⅡ建立工程文件,編輯上述代碼并進行仿真,仿真結果如圖3所示,輸出DC碼的前沿與CLR信號同步,參考標志在連續兩個位置標示符后開始發送時間數據,符合IRIG-B碼中直流碼標準要求。

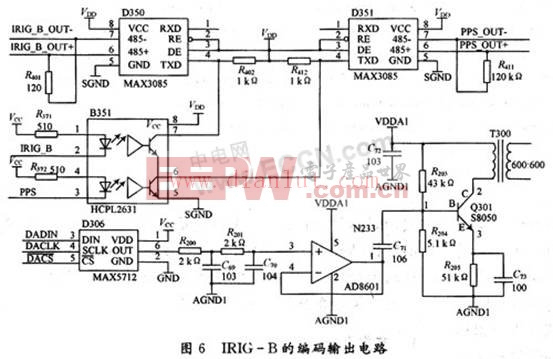

IRIG-B碼是標準時間碼信號。由數字處理器通過I/O向數字邏輯電路實時刷新當前時間數據(IRIG-B精確到秒),FPGA經內部邏輯電路產生標準IRIG-B(DC)碼,其時間的起點與GPS時間脈沖對齊,并通過隔離差分驅動向遠程提供時間信息。

5 結論

仿真和實踐結果均表明,該編碼器可以產生穩定、可靠、連續的IRIG-B DC碼,與秒基準信號精確同步,同步誤差小于1μs,已成功運用到測控設備上。

fpga相關文章:fpga是什么

脈寬調制相關文章:脈寬調制原理

評論