基于FPGA的ARM圖像縮放器的實現

ARM是目前全球最大的嵌入式芯片技術的IP提供商,其所擁有的IP已經成為眾多芯片設計公司采納的一種技術標準和開發平臺。所以基于ARM 內核的SoC已經成為嵌入式處理器的開發重點,可通過ARM實現LCD控制器來完成對嵌入式LCD屏的控制。如果利用TFT屏支持顯示,其圖像分辨率存在局限性,因此通過搭建一個FPGA平臺實現圖像縮放器功能外接LCD顯示器,完成ARM信號的擴展顯示。同時FPGA也能完成對ARM平臺產生的圖像信號進行驗證和仿真,以測試其功能和時序的正確性。XGA顯示器因其顯示量大,輸出形式多樣等特點已經成為目前大多數設計中的常用輸出設備,因此本文針對ARM產生的VGA信號通過插值算法對其擴展為XGA標準信號。

本文引用地址:http://www.104case.com/article/189620.htm1 VESA標準中的VGA與XGA時序

視頻電子標準協會(VESA)是非盈利國際組織,主要制定個人電腦、工作站以及消費電子類產品在視頻接口標準,因此本文所設計的VGA與XGA的時序均按照VESA標準設計。

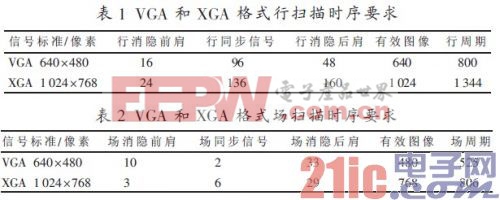

顯示器通常采用逐行掃描的方式,每一幀圖像按順序一行接著一行連續掃描而成,掃描的過程中由水平同步信號HSYNC和垂直同步信號VSYNC來控制掃描。行掃描和場掃描的時序圖如圖1所示,其行掃描和場掃描的時序要求如表1、表2所示。

圖1 行掃描時序和場掃描時序

2 系統整體設計

2.1系統框圖

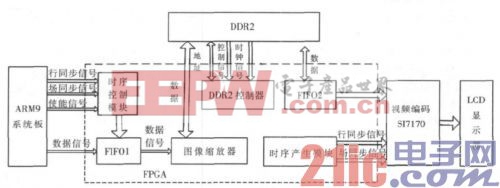

系統設計的數據源是來自ARM9系統板的視頻信號,其格式為VESA標準的VGA信號。數據源進入FPGA后先進行圖像縮放的處理,把輸入的有效像素數據利用算法對其進行處理,期間的處理數據利用FIFO與DDR2進行緩存,然后把處理后的圖像數據按照XGA時序送入視頻編碼芯片,最后送入顯示器顯示。其中FPGA內部設計分為時序控制模塊、時序產生模塊、FIFO模塊、圖像縮放器模塊以及DDR2 SDRAM控制器模塊,如圖2所示。

圖2 系統原理框圖

2.2 硬件實現

FPGA采用Altera的EP3C16F484C6芯片,該芯片具有15 408個邏輯單元,504 KB內存,56個乘法器和4個PLL鎖相環內核,最大支持346個I/O端口,系統時鐘最高為250 MHz。FPGA開發板采用了專門的視頻解碼編碼芯片,Silicon Image的視頻編碼芯片SI7170支持VGA到UVGA的格式標準,同時也支持HDTV格式的編碼。DDR2 SDRAM采用三星的K4T51163QC芯片, 其頻率支持267 MHz,本文選取為200 MHz。芯片容量為32 MB×16,實際上只要SDRAM滿足存儲2幀圖像的容量即可滿足本文設計要求[1]。完成轉換后的XGA信號所需的輸出時鐘為65 MHz,可由FPGA內部鎖相環產生。

fpga相關文章:fpga是什么

鎖相環相關文章:鎖相環原理

評論