高階QAM定時同步的MATLAB仿真及其FPGA實現

3 定點仿真到FPGA設計實現

定點仿真是在浮點仿真的基礎上,通過限定各個變量的精度,分析有限字長對系統性能的影響,權衡資源消耗和系統性能,從而得出各個信號合適的位寬,為FPGA實現做好準備。

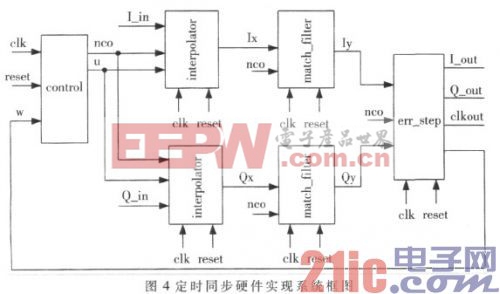

圖4是定時同步硬件實現的系統框圖。clk是I、Q兩路輸入信號的同步時鐘,也是主系統時鐘,此處為102.4 MHz(系統采樣率)。reset是全局同步復位信號,當其為有效電平時,步長w初始化為Ts/Ti,這里為0.5;分數間隔u可以初始化為任何值,這里取0;其余寄存器都初始化為0。I_in和Q_in是定時同步的兩路輸入信號,從整個接收機的角度來看是DDC模塊的輸出。I_out和Q_out是定時同步的輸出數據,送給接收機的均衡模塊。clkout是輸出數據的同步時鐘。control模塊就是1.4節中的插值控制器,當數控振蕩器溢出,插值控制信號nco為1,同時按式(3)更新分數間隔u;當數控振蕩器不溢出,則信號nco為0,分數間隔u保持原值。這兩個信號(nco和u)與I、Q兩路輸入信號一起送給interpolator模塊(插值濾波器),需要強調的是,nco信號也作為后面兩個模塊的控制信號,用以控制數據流動的節拍。兩路數據經過match_filter模塊(匹配濾波器)后進入err_step模塊,該模塊包括定時誤差提取和環路濾波器兩個部分,用以得到步長w的更新值然后反饋給control模塊進行下一輪的計算,并且對其輸入數據進行兩倍抽取得到定時同步的輸出信號。

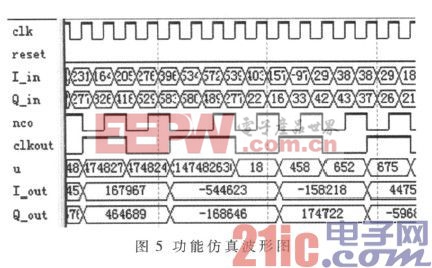

圖5是Quartus功能仿真波形圖,可以看出環路收斂前nco信號存在一定的抖動,導致輸出時鐘clkout并不是規則的時鐘信號,同樣存在抖動。環路內部的數據流動都是在nco信號的控制節拍下進行的。

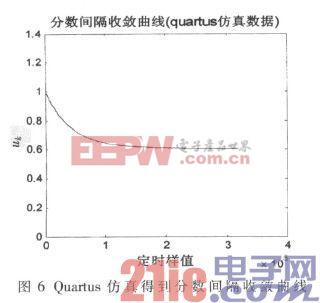

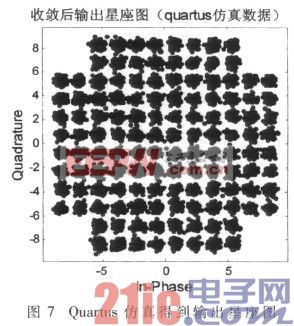

將Quartus 功能仿真后的波形數據讀取到MATLAB的工作空間中,可以得到分數間隔收斂曲線(圖6)和收斂后輸出星座圖(圖7),通過比較發現,Quartus功能仿真結果與MATLAB浮點仿真結果基本一致。

對于高階高碼率QAM調制系統,設計并實現了一種定時同步結構,該結構能夠提前獨立于載波同步單獨完成。MATLAB仿真和Quartus功能仿真結果表明,系統具有良好的性能。最后,通過時序分析,硬件系統的最高運行頻率可以達到200 MHz,完全滿足采樣率102.4 MHz的要求。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論