基于NIOSⅡ的GPS信息接收系統設計與實現

3 系統軟件設計

FPGA內部使用Quartus內嵌的工具SoPC Builder搭建NIOSⅡ處理器,并用Verilog硬件描述語言來描述FPGA內部電路結構,而μC/OS實時操作系統的植入及系統的控制程序則是由C語言編程完成的。

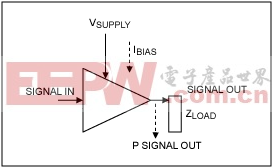

3.1 FPGA內部邏輯實現

首先構建NIOSⅡ處理器,包括一個CPU和它的內存單元、JTAG和UART部分,如圖3所示。本文引用地址:http://www.104case.com/article/189581.htm

從圖3中可以看出NIOS處理器和外圍設備及接口的大概結構,各部分通過Avalon總線連接起來,并可以自動分配地址和中斷。

根據設計對實時性的需要,其中NIOS軟核選擇NIOSⅡ/f,它占資源最多,但速度最快,并且功能最多;RS 232串口根據NMEA-0183協議,為了獲取GPS定位信息,必須將波特率設置為9 600 b/s,數據位設置為8 b,停止位設置為1 b,校驗為設置為無。

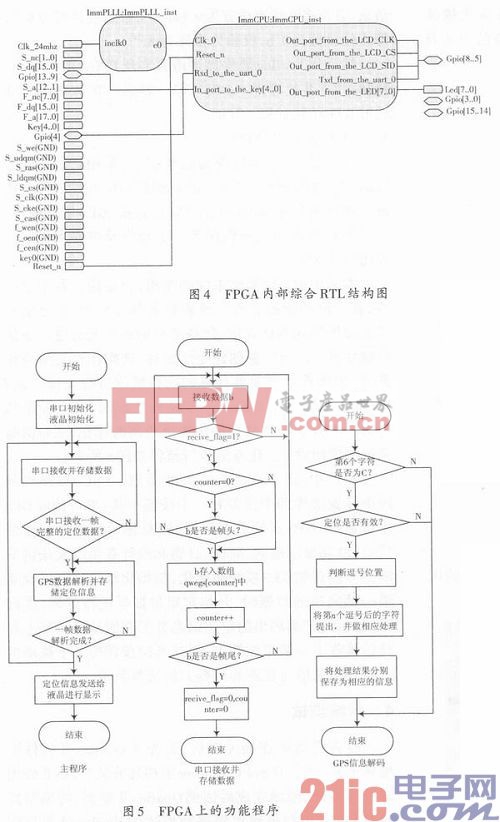

然后用Verilog硬件描述語言實現FPGA內部邏輯,包括NIOSⅡ處理器、鎖相環等。最后,FPGA內部綜合后的RTL結構如圖4所示。

評論